|

查看:

1143

|

回复:

0

|

存储单元结构分类

|

是酒窝啊

196

主题

231

回复 |

1#

电梯直达

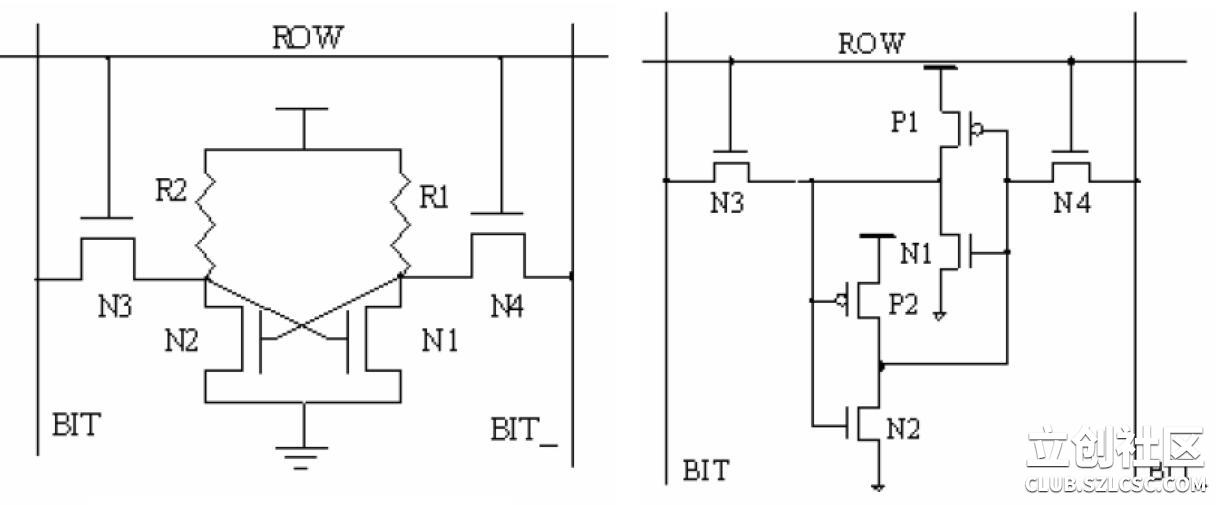

静态RAM的基本构造块是SRAM存储单元。通过升高字线的电平触发存储单元,再通过位线对所触发的存储单元进行读出或写入。在静态CMOS存储器中,存储单元阵列将会占去整个存储器芯片面积的一半以上,在一些大容量的SRAM中,这个比例还要更大一些。因而减小存储单元的面积变得尤为重要。 在存储器中有大量的存储元,把它们按相同的位划分为组,组内所有的存储元同时进行读出或写入操作,这样的一组存储元称为一个存储单元。一个存储单元通常可以存放一个字节;存储单元是CPU访问存储器的基本单位. 从结构上分,CMOS SRAM 存储单元有电阻-晶体管结构(4T-2R 存储单元)和静态六管全互补结构(6T 存储单元)。 图1 4T-2R存储单元结构 图2 6T 存储单元结构 4T-2R 存储单元的存储器并非完全意义的CMOS 电路,它们的存储单元往往选用同一沟道的晶体管,而在外围电路的实现中采用了CMOS 电路;与6T 单元10 高速低功耗SRAM的设计与实现相比,采用单一沟道的存储单元不但会减少工艺的复杂度,而且能有效的减小芯片面积,这主要是因为不需要额外的面积来隔离N-well 或P-well。 六管存储单元采用了一根单一的字线、一根位线和一根反相的位线。互为反相的两根位线通常称为 bit和bit_。单元中包括了一对交叉耦合的反相器,并且每根位线连接了一个存取晶体管。一对互补的数据存储在交叉耦合的反相器上。如果数据受到轻微的干扰,由回路构成的正反馈将使数据恢复到VDD或GND。

宇芯电子主要产品线有静态随机存储器SRAM,非易发性存储器MRAM,伪静态存储器PSRAM等多种类型随机记忆体及微控制器MCU等半导体产品,189-2655-4009

|

|

发表于2020-04-30 16:59:08

发表于2020-04-30 16:59:08

收藏

收藏