|

查看:

2188

|

回复:

3

|

采用分级字线结构可提高SRAM读写速度及降低电路动态功耗

|

是酒窝啊

196

主题

231

回复 |

1#

电梯直达

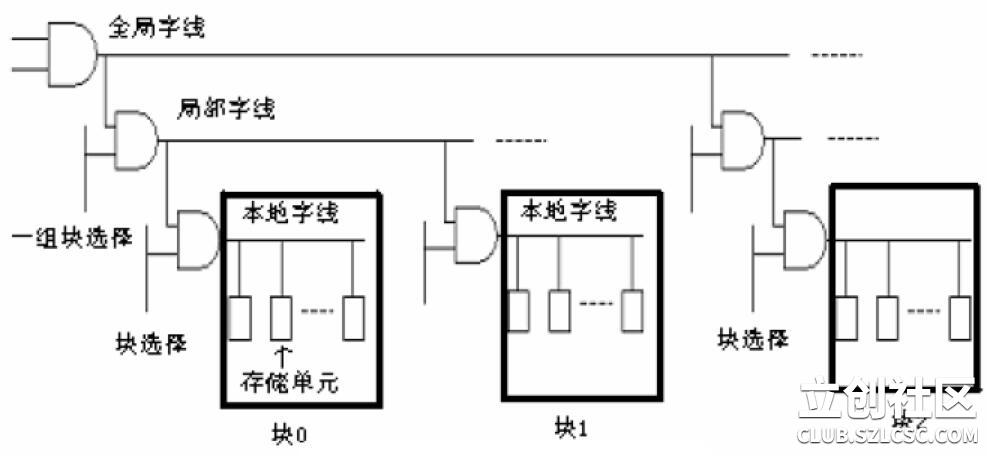

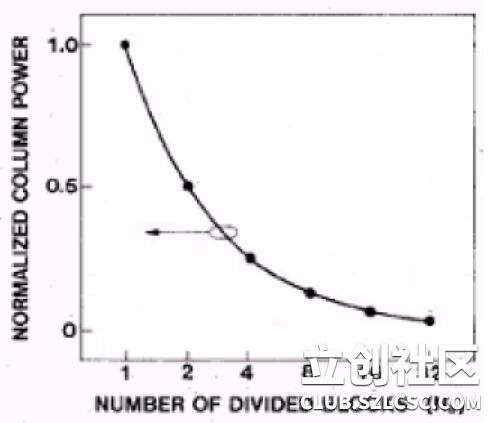

采用分级字线结构的存储器将整个存储阵列划分为若干个相同的子阵列。与非分级字线结构相比,它需要采用多级的字线译码才能完成对存储单元的寻址。如图1所示,整个电路采用层次化字线的多分割阵列结构。 图1 分级字线结构 采用层次化字线分割结构不仅能提高工作速度,而且能大大降低功耗。这是因为字线分割结构使原本同时被激活的存储单元变为只有被选中的块内的存储单元被激活。 具体工作为:假设将一条字线分为n段,若原来每条字线带Nc个单元,则分割后每段字线只带Nc/n个单元,字线长度也减小为原来的1/n。对于很大容量的存储器,并不是简单地把字线分段,而是采用如图1 所示的分级字线结构,即把单元阵列在字线方向分成很多小块,使每个小块中的局部字线缩短,所带单元数目减少。一定数目的局部字线(WL)通过块选择控制连接到次全局字线(SWL)上,几条次全局字线再通过选择控制门连接到全局字线(GWL)。其中全局字线由行地址的高几位经全局字线译码器译码产生,它将贯穿整个存储阵列来驱动各个子模块的块内字线译码器;而块内字线则由全局字线、块选信号以及低几位的行地址相与产生,块内字线直接与存储单元的存取管相连,控制存储单元是否选通。图2通过SPICE模拟仿真给出了字模块个数与功耗的关系。 图2 子模块个数与功耗的关系 对于4Kb SRAM,最简单的二维阵列划分为:256 行×16 列,假设Cbl为每个存储单元相对于位线的寄生电容,Cwl为每个存储单元相对于字线的寄生电容,则对于上述的二维阵列结构来说,在忽略位线、字线自身寄生电容的情况下,每根位线上的总负载电容为256×Cbl,每根字线的总负载电容为16×Cwl。若将整个阵列分为2 个128×16b的子阵列,且各阵列都配有行、列译码单元及预充电路,使它们相互独立的话,位线负载减少为128×Cbl,而块内字线上的负载也减小为16×Cwl,因此块内字线与位线上的延迟特性会得到很大的改善。由于存储单元的位线上都配有预充电电路,预充电操作在整个芯片的功耗中占有相当大的比重。采用分级字线结构,则在读写操作时只需对其中的一个子阵列进行充电操作,以本设计为例,每次读写操作进行充/放电的电容负载仅为128×16×2×Cbl+16×Cwl=4096×Cbl+16×Cwl,而对于256 行×512 列的阵列来说,相应的充/放电负载电容为:1024×64×2×Cbl+64×Cwl=131072×Cbl+64×Cwl。由静态CMOS电路功耗的近似表达式:P = C × (VDD) × f 可以看出,采用分级字线结构不仅提高了SRAM 的读写速度,而且降低了电路的动态功耗。

宇芯电子主要产品线有静态随机存储器SRAM,非易发性存储器MRAM,伪静态存储器PSRAM等多种类型随机记忆体及微控制器MCU等半导体产品,189-2655-4009

|

是酒窝啊

196

主题

231

回复 |

2#

采用分级字线结构不仅提高了SRAM 的读写速度,而且降低了电路的动态功耗。

宇芯电子主要产品线有静态随机存储器SRAM,非易发性存储器MRAM,伪静态存储器PSRAM等多种类型随机记忆体及微控制器MCU等半导体产品,189-2655-4009

|

是酒窝啊

196

主题

231

回复 |

3#

采用层次化字线分割结构不仅能提高工作速度,而且能大大降低功耗。这是因为字线分割结构使原本同时被激活的存储单元变为只有被选中的块内的存储单元被激活。

宇芯电子主要产品线有静态随机存储器SRAM,非易发性存储器MRAM,伪静态存储器PSRAM等多种类型随机记忆体及微控制器MCU等半导体产品,189-2655-4009

|

是酒窝啊

196

主题

231

回复 |

4#

宇芯电子主要产品线有静态随机存储器SRAM,非易发性存储器MRAM,伪静态存储器PSRAM等多种类型随机记忆体及微控制器MCU等半导体产品,189-2655-4009

|

|

发表于2020-05-19 16:28:59

发表于2020-05-19 16:28:59

收藏

收藏