|

查看:

774

|

回复:

0

|

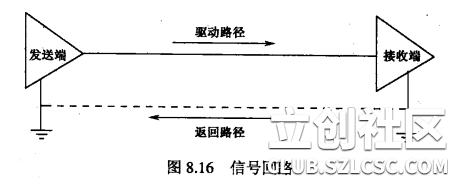

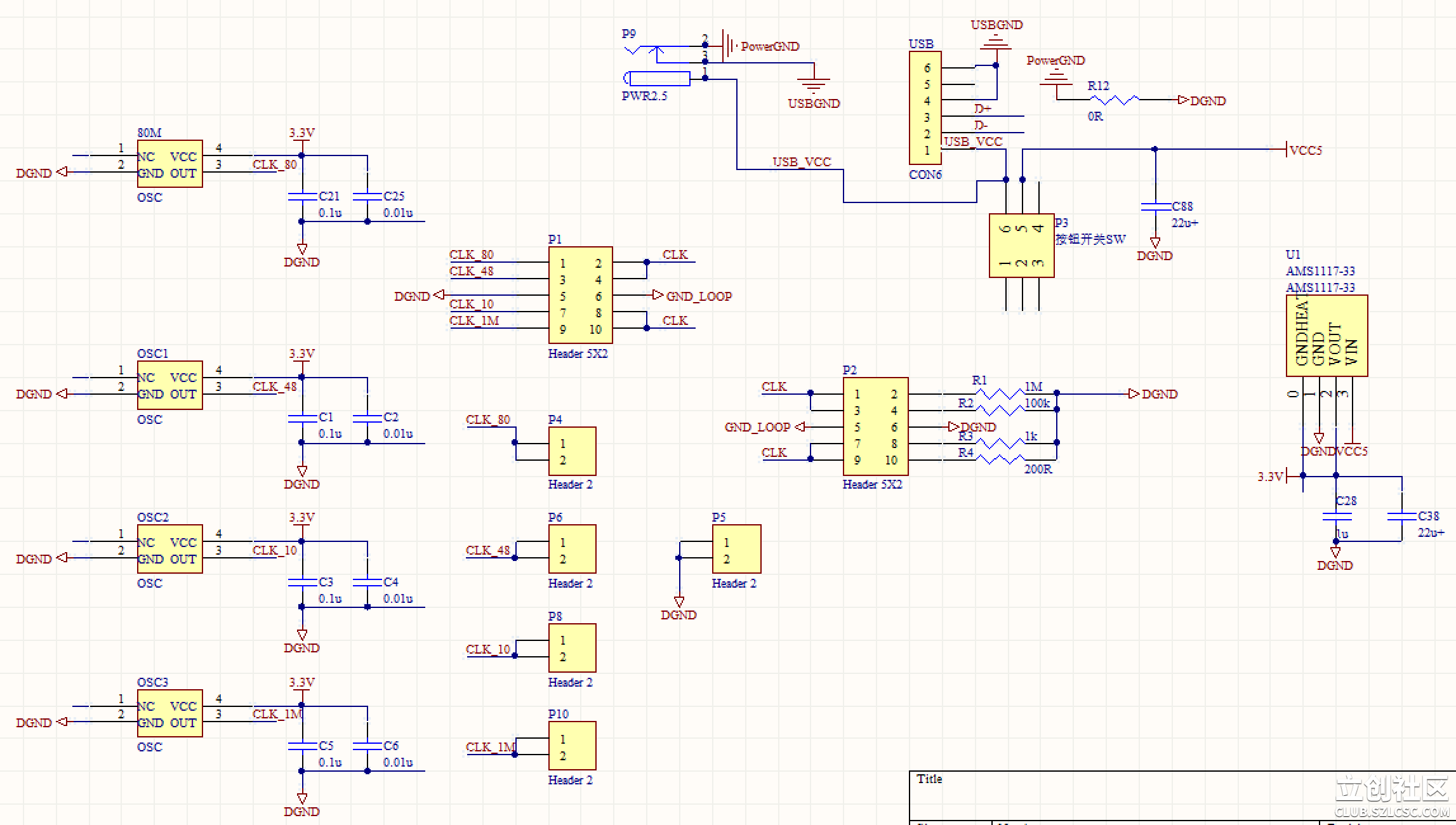

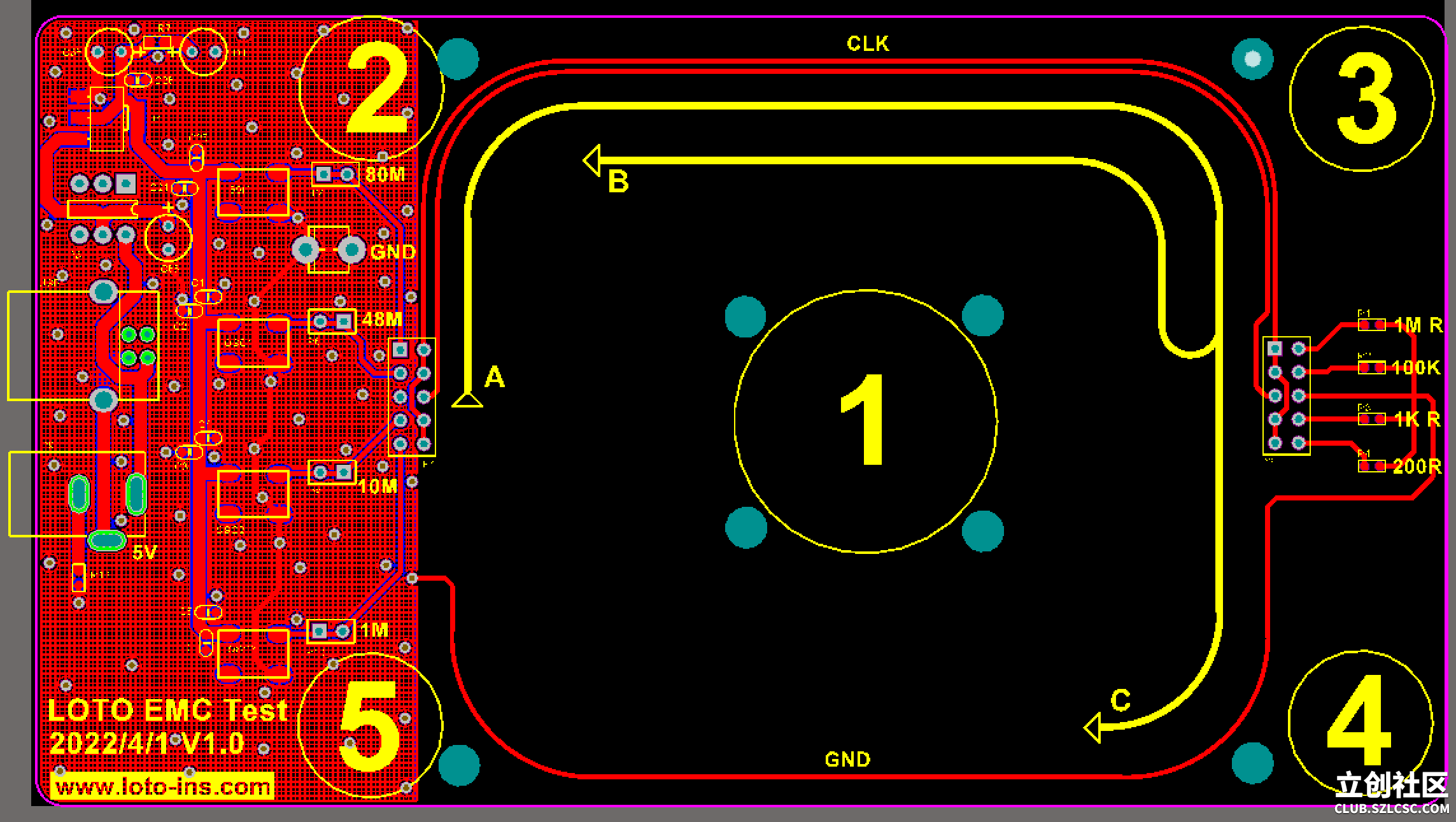

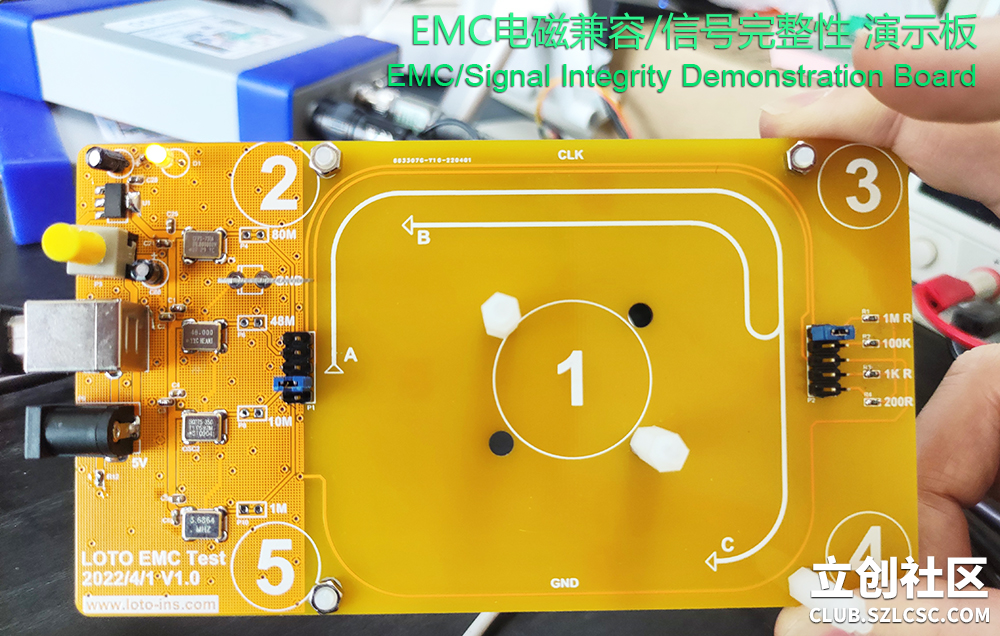

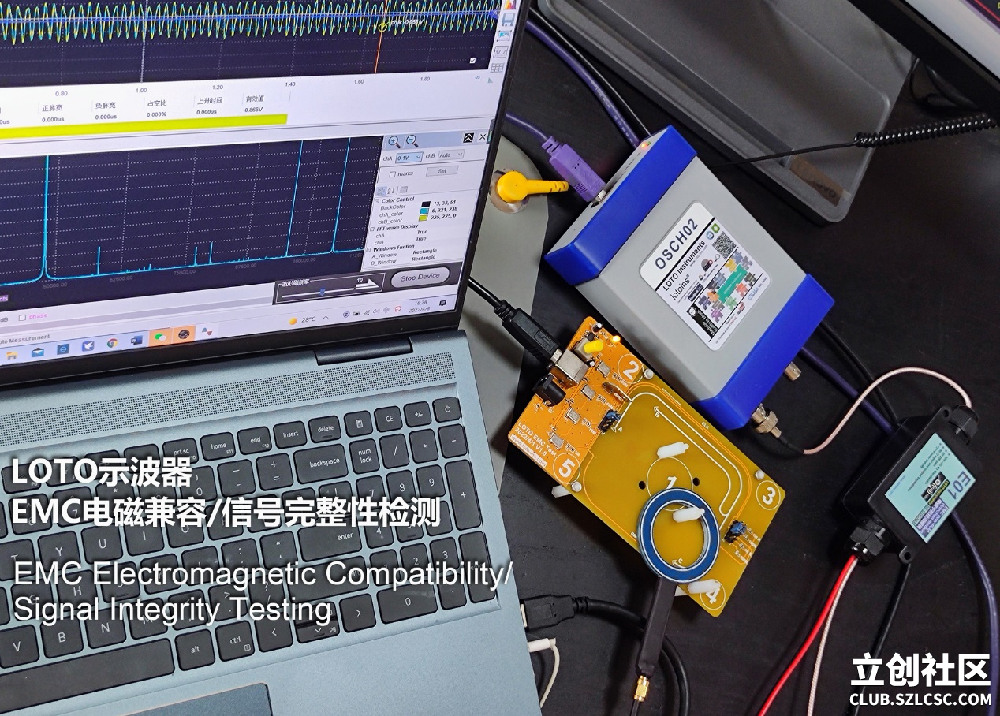

EMC信号完整性落地实测1---走出玄学

|

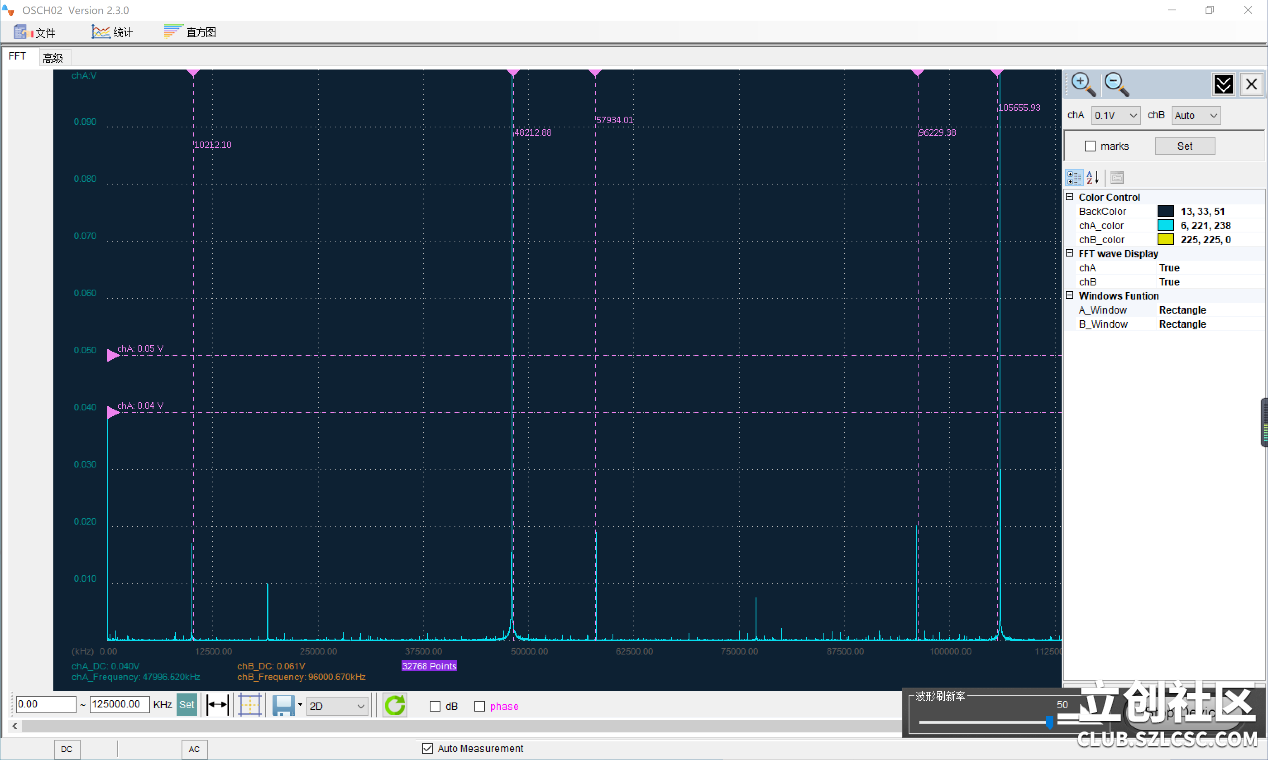

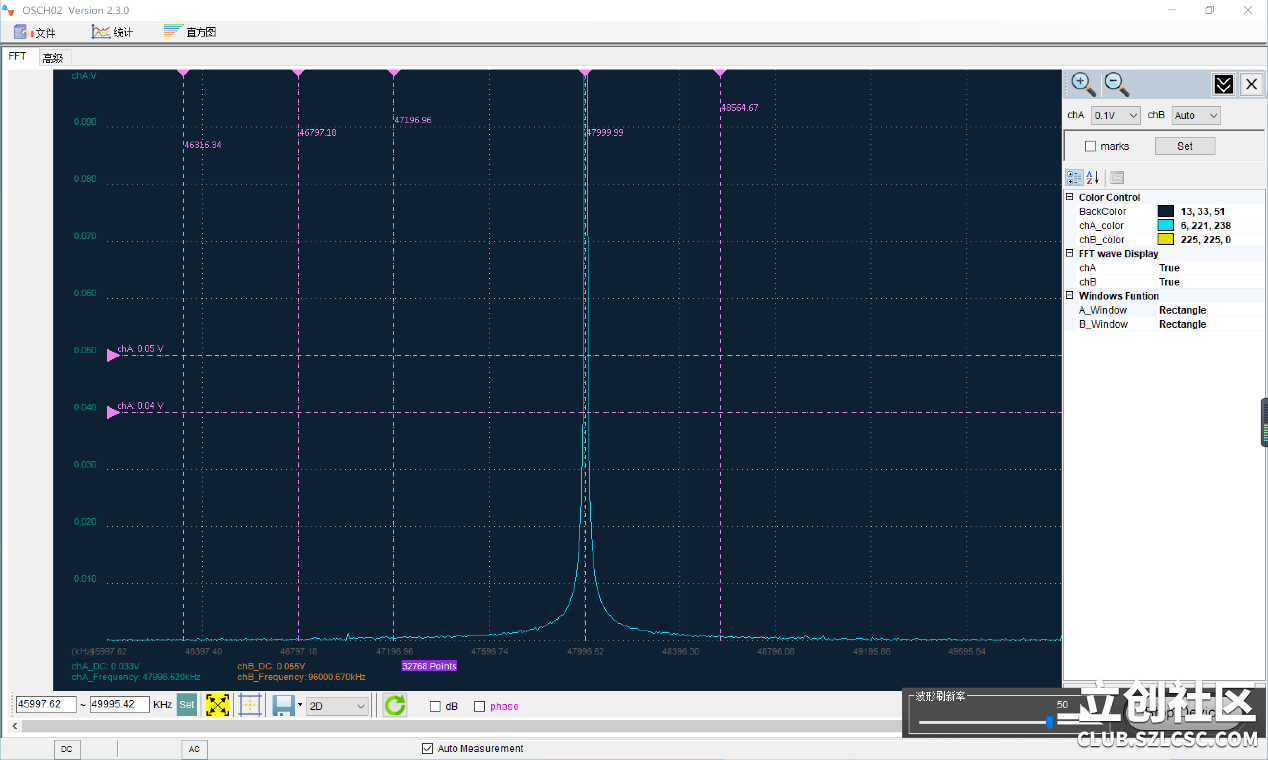

LOTO

69

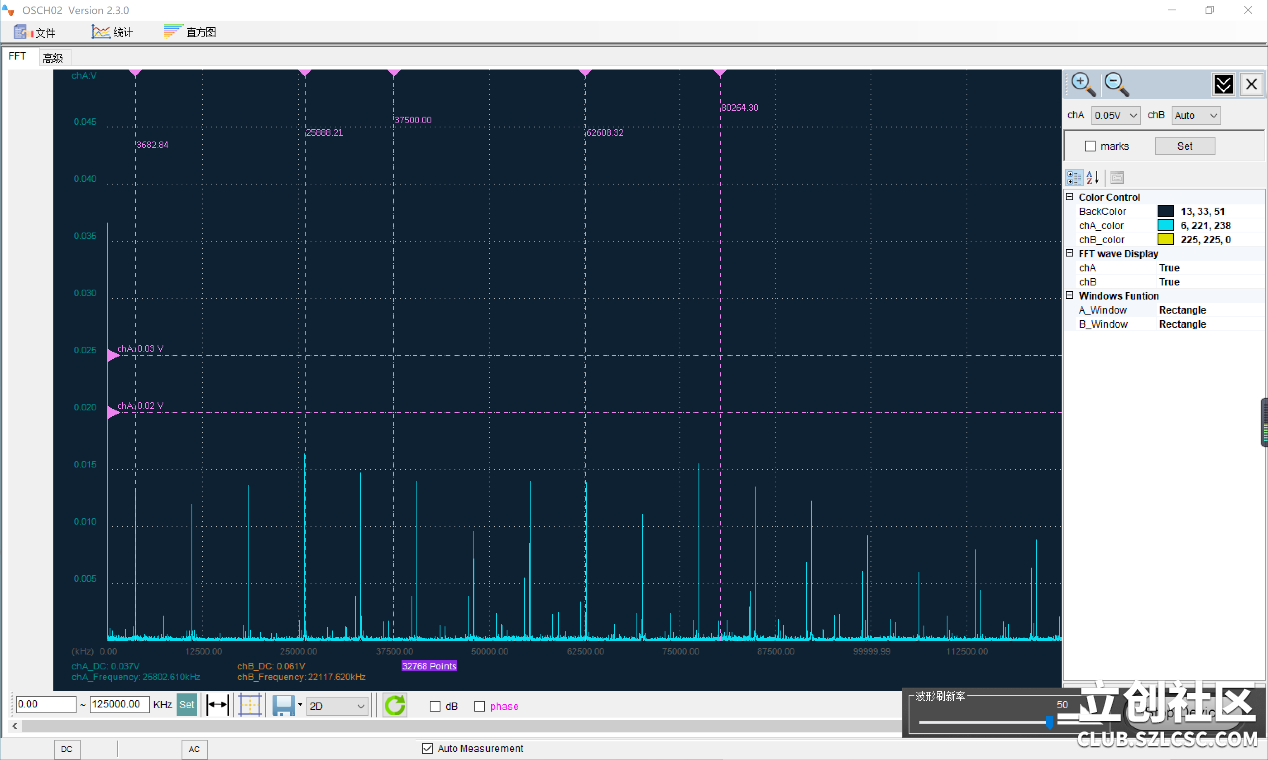

主题

9

回复 |

1#

电梯直达

EMC信号完整性落地实测1---走出玄学

无论我们从51单片机,STM32电路,运放,传感器,ADC采集还是可控硅晶闸管等等电源电路跨入到电子工程师的行业,我们通常会长时间处于低频的电子电路设计调试阶段,通常我们处理的是几百Hz或者几K Hz的信号通路。偶尔会有RS232,RS485,IIC,SPI或者CAN总线之类的通讯让我们的PCB经历几百K Hz的信号。这些其实涵盖了大部分的电子应用场景,我们在这个阶段更多的关注电路功能的实现,并没有也不太需要考虑信号完整性或者EMC的问题。 总有一天我们会在新的项目中发现我们遇到了一些瓶颈。有时候通讯会莫名其妙的通讯错误,有些PCB板子会莫名其妙的有很大的干扰,达到M级信号的板子按以前的布线习惯变得不再稳定可靠。这时,阻碍电子工程师进阶的EMC和信号完整性问题摆在了我们面前。如果你遇到了类似的问题,那么恭喜,说明你已经到了另一个新台阶了。 EMC和信号完整性是独立于电子电路功能设计的另一门学问了,我们可以找到很多这方面的资料,大部分会告诉我们理论知识和经验准则。比如,在高速信号的情况下,电容电阻都不再单纯的看做是电容和电阻了,甚至连路径上的过孔也会有影响。PCB布线不再是布通就可以了,还需要考虑信号流动的路径;布线和布线之间的间距以及下方是否铺地也要考虑了,甚至关键的信号布线长度都需要考虑等等。这些对于射频工程师来说都是需要掌握的基本技巧,对于其他领域的广大电子工程师来说,这些就是高手和普通选手之间的进阶知识了。 对于大多数工程师来说,EMC和信号完整性的一些经验法则,近乎玄学,我们知道要按照这条法则去做,但是并不直观的知道这样做和不这样做差别多大,没有直观的感受。因为这些法则的总结是靠非常昂贵的专业设备,在不计成本的实验中总结的,我们普通大众电子工程师是没有机会去做实验感受和吸收的,只能被动接受这样的理论指导,完全没有其他电子电路知识那样的体验。 我们通过LOTO虚拟示波器和它的EMC测试模块,对一些重要的EMC和信号完整性经验法则进行直观的落地实测,方便大家直观看到,这些法则的效果,打破玄学,加深理解。 我们动手的第一条法则:信号发射出去的驱动路径和回流到地构成的返回路径,围绕出来的环路面积越小越好。环路面积越大,造成的噪声耦合和EMI电磁干扰越严重。 如下图所示: 为了落地实测,我们简单做了一个实验板,原理图和PCB如下所示,有需要的同学可以直接跟我要源文件: 板子使用USB供电或者外接5V电源供电,一个电源开关,放了4个3.3V的有源运放,分别是80M,48M,11M,3.68M。当然你可以放自己想要观测的频率的晶振。这些晶振通过跳线选择一个晶振频率输出,沿着A出发,经过2号区域,到3号区域,然后经过4号区域返回到5号区域。在PCB右侧的跳线可以选择这个晶振信号的负载电阻是多大,从1M到200欧可以选择一个。这样我们可以直观看到,一个高速信号,频率是跳线选择的晶振频率,在PCB上驱动了一个跳线选择的负载电阻,形成了PCB丝印上的A->C的环路。我们也可以在两个跳线上通过跳线把沿着信号布线下面的一条地线连接通,那么信号的环路变成了A->B,比原来的A->C小了环路面积小了很多。我们看下实物: 我们选择48M晶振,然后使用负载100K,使用A->C环路,LOTO虚拟示波器OSCH02,以及E01模块,我们实测1区域的EMC信号完整性的情况,搭建场景如下: 我们在测试板的1号区域,测得EMI的频谱如下所示,可以看到有一个幅值非常大的48MHz的电磁辐射,幅值超过了0.15V: 我们可以以48M为中心频率,查看细节: 我们保持其他不变,通过接地跳线把信号的地回路改为A->B,同样在测试板的1号区域,测得EMI的频谱如下所示,可以看到48MHz的电磁辐射明显减小,幅值变为0.073V: 同理,我们测下3.68M晶振的也是类似的情况,如下图所示,规律也是环路面积大,EMI电磁干扰强度就大,不同的是,3.68M晶振的频谱图里会看到很多谐波分量,这是由于我们这个窗口的监测范围是125M,在这个范围内,可以显示3.68M的多次谐波。晶振本身是近似方波的信号,所以会有很多次谐波,只是之前测的48M的多次谐波超出了窗口观测范围没有看到而已。高次谐波并不是客观存在的,他是FFT的数学表达,我们在观测EMC的频谱时要注意这一点。 我们很直观的看到,同一个高频信号,在PCB电路板上不同的路径造成不同的环路面积的情况下,截然不同的EMI电磁干扰强度。我们不仅仅验证信号完整性布线准则的最小环路面积要求,也可以用LOTO示波器+E01电磁兼容扩展检测模块来直接测试我们已有的电路板的电磁兼容EMC问题。 |

|

发表于2022-04-13 11:14:12

发表于2022-04-13 11:14:12

收藏

收藏