|

查看:

2306

|

回复:

12

|

求助,利用梁山派EXMC模拟8位并口8080时序数据之间不连续出现杂乱信号

|

|||

靠谱的成年人

1

主题

7

回复 |

1#

电梯直达

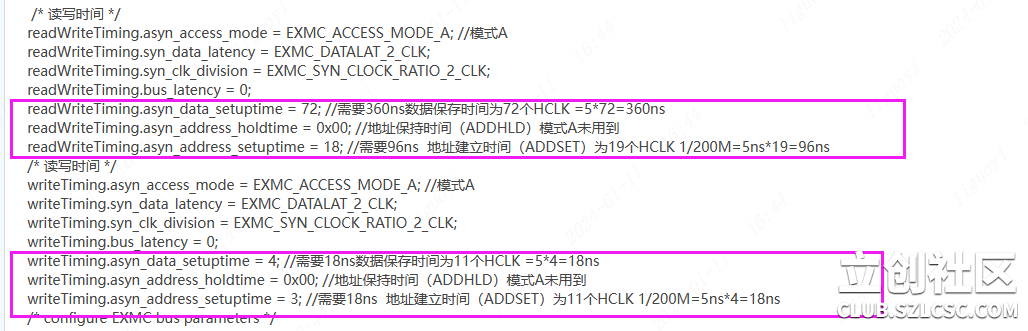

最近在使用梁山派驱动一块LCD屏幕,同时也准备学习一下EXMC外设,使用的屏幕是8080驱动。于是从立创开发板提供的例程里面找到了关于16位并口的LCD驱动代码,下面是移植来的初始化代码: void exmc_gpio_init(void) { rcu_periph_clock_enable(RCU_GPIOD); rcu_periph_clock_enable(RCU_GPIOE); rcu_periph_clock_enable(RCU_GPIOG); gpio_af_set(GPIOD, GPIO_AF_12, GPIO_PIN_0|GPIO_PIN_1 |GPIO_PIN_4|GPIO_PIN_5|GPIO_PIN_8|GPIO_PIN_9|GPIO_PIN_10|GPIO_PIN_14|GPIO_PIN_15); // EXMC功能 gpio_af_set(GPIOE, GPIO_AF_12, GPIO_PIN_7|GPIO_PIN_8 |GPIO_PIN_9|GPIO_PIN_10|GPIO_PIN_11|GPIO_PIN_12|GPIO_PIN_13|GPIO_PIN_14|GPIO_PIN_15); // EXMC功能 gpio_af_set(GPIOG, GPIO_AF_12, GPIO_PIN_0|GPIO_PIN_12); // EXMC功能 gpio_mode_set(GPIOD, GPIO_MODE_AF, GPIO_PUPD_PULLUP,GPIO_PIN_0|GPIO_PIN_1 |GPIO_PIN_4|GPIO_PIN_5|GPIO_PIN_8|GPIO_PIN_9|GPIO_PIN_10|GPIO_PIN_14|GPIO_PIN_15); gpio_output_options_set(GPIOD, GPIO_OTYPE_PP, GPIO_OSPEED_50MHZ,GPIO_PIN_0|GPIO_PIN_1 |GPIO_PIN_4|GPIO_PIN_5|GPIO_PIN_8|GPIO_PIN_9|GPIO_PIN_10|GPIO_PIN_14|GPIO_PIN_15); gpio_mode_set(GPIOE, GPIO_MODE_AF, GPIO_PUPD_PULLUP,GPIO_PIN_7|GPIO_PIN_8 |GPIO_PIN_9|GPIO_PIN_10|GPIO_PIN_11|GPIO_PIN_12|GPIO_PIN_13|GPIO_PIN_14|GPIO_PIN_15); gpio_output_options_set(GPIOE, GPIO_OTYPE_PP, GPIO_OSPEED_50MHZ,GPIO_PIN_7|GPIO_PIN_8 |GPIO_PIN_9|GPIO_PIN_10|GPIO_PIN_11|GPIO_PIN_12|GPIO_PIN_13|GPIO_PIN_14|GPIO_PIN_15); gpio_mode_set(GPIOG, GPIO_MODE_AF, GPIO_PUPD_PULLUP,GPIO_PIN_0|GPIO_PIN_12); gpio_output_options_set(GPIOG, GPIO_OTYPE_PP, GPIO_OSPEED_50MHZ,GPIO_PIN_0|GPIO_PIN_12); } void exmc_init(void) { exmc_gpio_init(); rcu_periph_clock_enable(RCU_EXMC); exmc_norsram_parameter_struct nor_init_struct; // EXMC参数结构体 exmc_norsram_timing_parameter_struct readWriteTiming; // EXMC时间参数结构体 exmc_norsram_timing_parameter_struct writeTiming; // EXMC时间参数结构体 /* 读写时间 */ readWriteTiming.asyn_access_mode = EXMC_ACCESS_MODE_A; //模式A readWriteTiming.syn_data_latency = EXMC_DATALAT_2_CLK; readWriteTiming.syn_clk_division = EXMC_SYN_CLOCK_RATIO_2_CLK; readWriteTiming.bus_latency = 0; readWriteTiming.asyn_data_setuptime = 72; //需要360ns数据保存时间为72个HCLK =5*72=360ns readWriteTiming.asyn_address_holdtime = 0x00; //地址保持时间(ADDHLD)模式A未用到 readWriteTiming.asyn_address_setuptime = 18; //需要96ns 地址建立时间(ADDSET)为19个HCLK 1/200M=5ns*19=96ns /* 读写时间 */ writeTiming.asyn_access_mode = EXMC_ACCESS_MODE_A; //模式A writeTiming.syn_data_latency = EXMC_DATALAT_2_CLK; writeTiming.syn_clk_division = EXMC_SYN_CLOCK_RATIO_2_CLK; writeTiming.bus_latency = 0; writeTiming.asyn_data_setuptime = 4; //需要18ns数据保存时间为11个HCLK =5*4=18ns writeTiming.asyn_address_holdtime = 0x00; //地址保持时间(ADDHLD)模式A未用到 writeTiming.asyn_address_setuptime = 3; //需要18ns 地址建立时间(ADDSET)为11个HCLK 1/200M=5ns*4=18ns /* configure EXMC bus parameters */ nor_init_struct.norsram_region = EXMC_BANK0_NORSRAM_REGION3; // FSMC_NORSRAMInitStructure.FSMC_Bank = FSMC_Bank1_NORSRAM4;// FSMC_Bank1_NORSRAM4;// 这里使用NE1 ,也就对应BTCR[6],[7]。 nor_init_struct.address_data_mux = DISABLE; // 不复用数据地址 nor_init_struct.memory_type = EXMC_MEMORY_TYPE_SRAM; // FSMC_MemoryType_SRAM; //SRAM nor_init_struct.databus_width = EXMC_NOR_DATABUS_WIDTH_8B; nor_init_struct.burst_mode = DISABLE; nor_init_struct.nwait_polarity = EXMC_NWAIT_POLARITY_LOW; nor_init_struct.asyn_wait = DISABLE; nor_init_struct.wrap_burst_mode = DISABLE; nor_init_struct.nwait_config = EXMC_NWAIT_CONFIG_BEFORE; nor_init_struct.memory_write = ENABLE;// 存储器写使能 nor_init_struct.nwait_signal = DISABLE; nor_init_struct.extended_mode = ENABLE; // 读写使用不同的时序 nor_init_struct.write_mode = EXMC_ASYN_WRITE; nor_init_struct.read_write_timing = &readWriteTiming;//读写时序 nor_init_struct.write_timing = &writeTiming;//写时序 exmc_norsram_init(&nor_init_struct); //初始化FSMC配置 /* enable the EXMC bank0 NORSRAM */ exmc_norsram_enable(EXMC_BANK0_NORSRAM_REGION3); // 使能BANK1 } 对例程里面的16位数据格式改成了8位数据格式,其他没变;

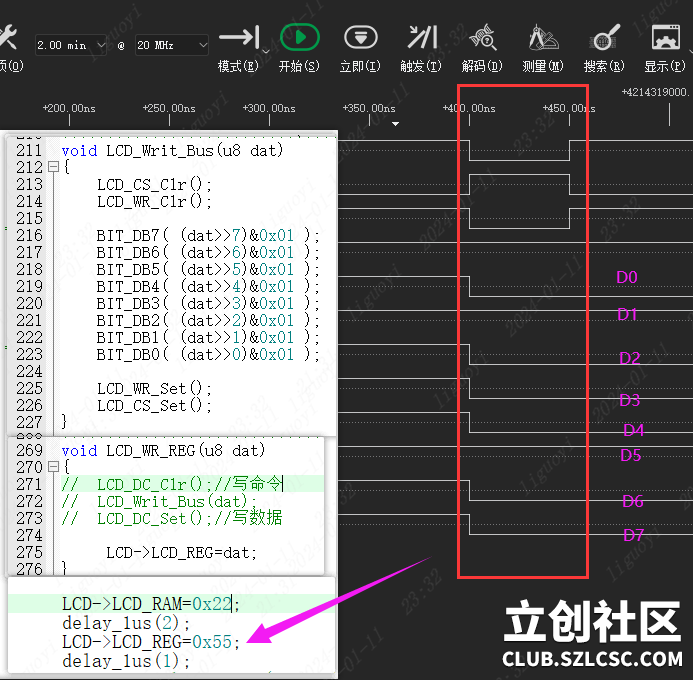

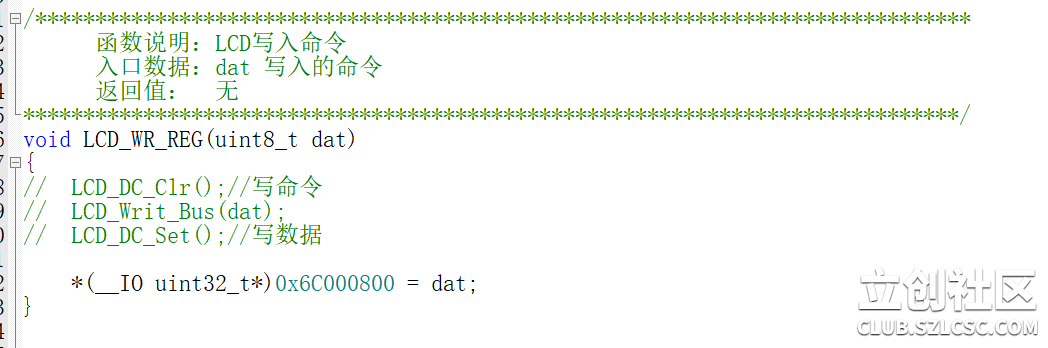

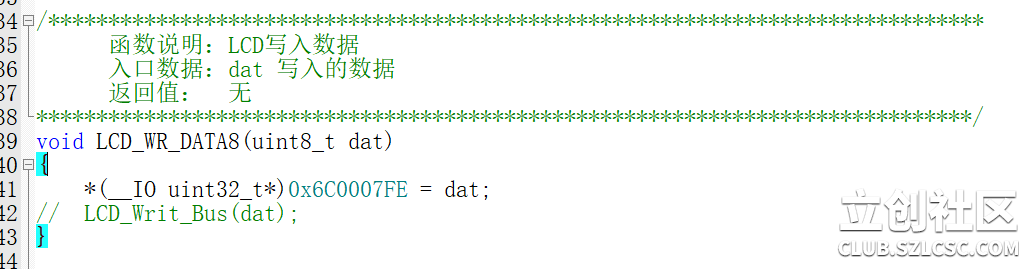

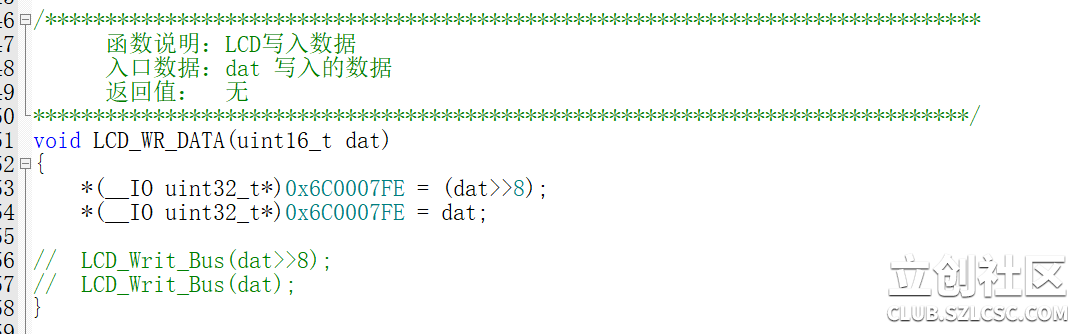

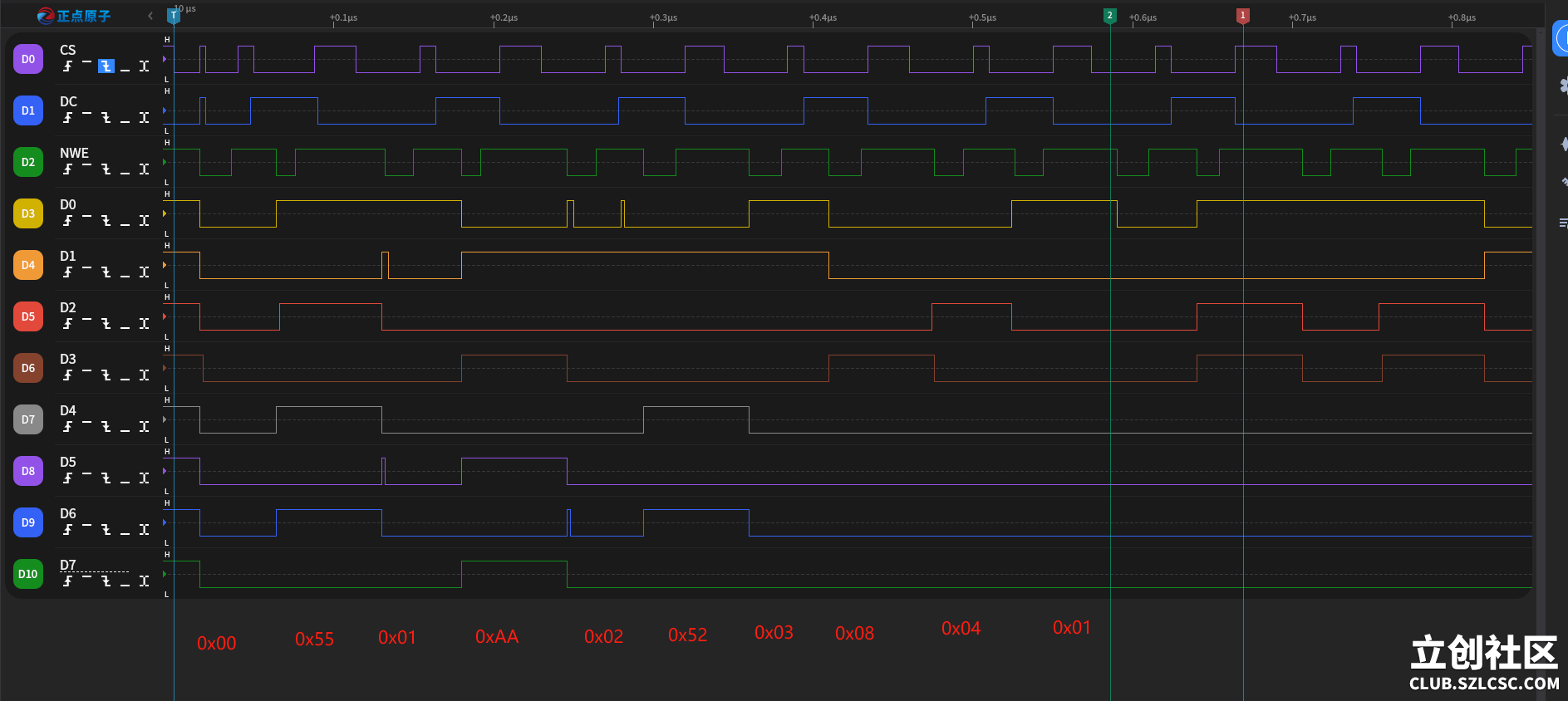

以上是编写的三个写入函数。并尝试发送以下数据测试波形情况发现发送的两个数据之间出现一段不规律的杂乱信号: 可以发现每一个正确数据之后总会发送一些0数据,然而运行梁山派提供的16位8080并口例程则可以正确发送,一下是梁山派例程运行结果,只抓取低8位数据验证: 向各位大佬求助,我的代码问题出在了哪里呀 |

|||

老怪鸽但不鸽

6

主题

22

回复 |

2#

你是怎么接线的呢?使用8位的数据地址线不会偏移,而梁山派上的扩展接口是地址线是EXMC_A10,所以写地址应该是3FE,读地址是400

|

|||

老怪鸽但不鸽

6

主题

22

回复 |

4#

那修改初始化代码中的读写时间,根据屏幕的读写时序来计算 |

|||

老怪鸽但不鸽

6

主题

22

回复 |

8#

现在越看越像是被开发板上的SDRAM干扰了

|

|||

老怪鸽但不鸽

6

主题

22

回复 |

10#

确定是只修改了16位数据位那里,修改为8位吗? 我这边飞线测测

|

|||

老怪鸽但不鸽

6

主题

22

回复 |

12#

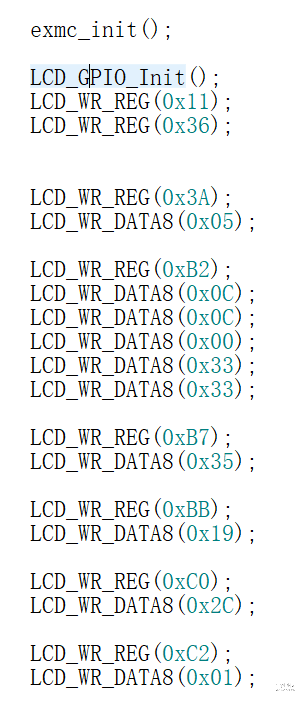

1. 实测,当处于8位数据宽度时,写命令地址0X000003FE,写数据地址0X00000400,A10引脚才可以实现电平变化;

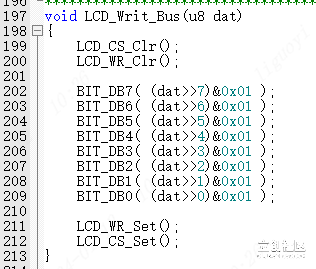

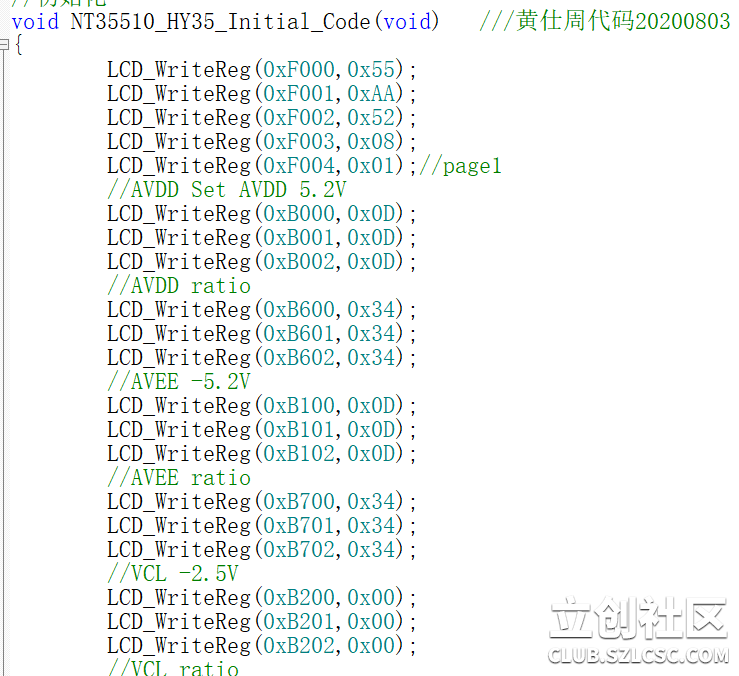

2. 关于两个数据之间出现一段不规律的杂乱信号,我使用梦源逻辑分析仪在 10MHz 下抓取数据确实有这个现象,但当使用 20MHz 时,没有出现杂波。 3. 使用IO模拟8080时序可以控制8位并口LCD; 时序源码:  时序:从上到下的时序线分别为 CS DC WR RD D0~D7  使用8位EXMC模拟8080无法控制8位并口LCD; 源码:  时序图:时序图的线序同上,但是发现数据线的时序过早拉低; 使用16位EXMC模拟8080驱动8位并口LCD,将高位省略只使用低位即可驱动; |

|

发表于2024-01-09 19:07:58

发表于2024-01-09 19:07:58

收藏

收藏