|

查看:

2627

|

回复:

3

|

Ti M0开发板测评报告+无刷电机FOC控制SVPWM波输出测试

|

HoneyFox

1

主题

1

回复 |

1#

电梯直达

Ti M0开发板测评报告+无刷电机FOC控制SVPWM波输出测试 最近有Ti原厂来公司推MSPM0系列芯片,主要用于直流无刷电机驱动,目前样板在打样中,Ti原厂帮忙申请的LP-MSPM0G3507开发板还在新加坡发货中,目前还没收到。正好立创有这个Ti M0开发板测评活动,第一时间就申请了。申请完之后就没放在心上了,以为不会被选上的,结果1月11日收到短信通知,当天就给发货了,发的顺丰快递,第二天就收到板子了,不得不说立创的效率还是可以的。

1.整体使用评价

如上图所示,我收到的是一块MSPM0G3507的扩展板,带有Flash,热敏电阻电路,光电传感器电路,作为电机驱动开发,这些扩展其实用不上,不过有一说一,这开发板做工还是可以的。板子自带有一个USB转TTL串口,调试起来很方便,不需要自己再外挂一个USB转串口模块。不过用的芯片是CH340N,就是速率有点低,最高2M。接MCU上的UART0串口,这个串口官方手册给出的最高速率可以达到5M,如果是在电源域PD1的UART3,手册给出的最高速率是10M。对于电机控制调试来说,速率越高越好,可以观测的变量越多。因此在测试过程中没有使用开发板自带的USB串口,使用了一个高速USB串口模块通过UART3以8M的波特率进行通信,将变量通过串口DMA高速发送给上位机,上位机可以实时查看变量的变化情况。Ti 的M0系列MCU带有硬件加速器以及IQmath库,可以很方便的调用,方便电机驱动程序开发。相比大多数M0的芯片只能执行16位乘法来说,性能提升不少。另外MCU带有运放以及高速ADC,综合来说是一款比较适合做电机控制开发的MCU。

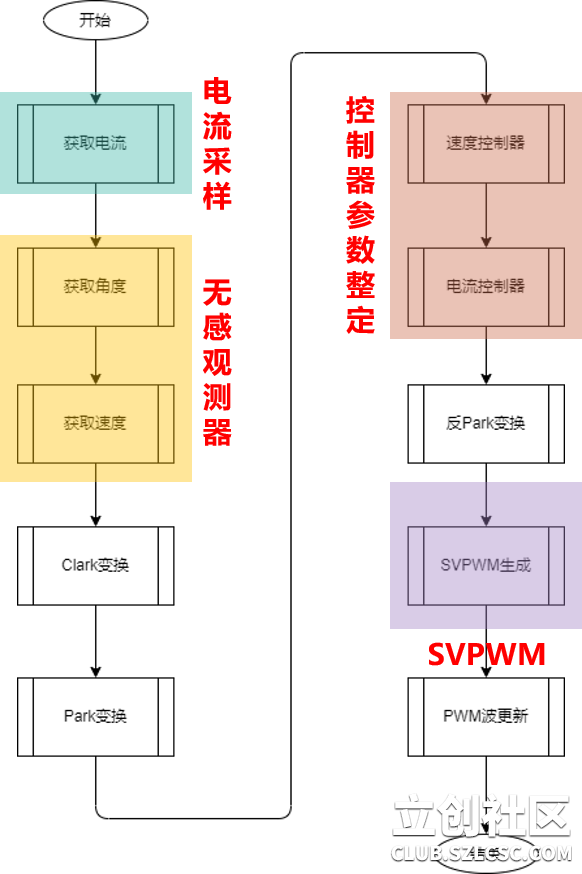

2.开发项目流程

一般的FOC控制流程如上图所示,因为开发板没有功率驱动电路,本次测试仅实现后部分程序测试,从反Park变换模块到PWM更新模型,在反park变换与SVPWM生成之间增加一个电压极限圆限制模块程序。由于之前没有使用过Ti的SysConfig配置软件,不是很会用。本来想自己手动配置外设,感觉配置起来太痛苦了,后面花了一两天的时间参照Ti的SDK里面的例程,总算把完整的外设配置给弄好了。包括时钟,ADC,PWM波形,UART,DMA等配置,详细的配置可以参考本贴附件的SysConfig文件。 本次测试使用的软件有:Keil,VSCODE,Ozone以及VOFA+。Keil用于创建项目工程;VSCODE用于代码编辑,并安装keil Assistant插件用于导入Keil创建的工程,并编译及下载;Ozone用于在线调试,Ozone也可看波形,就是采样速率有点慢,一般的Jlink限制1k的采样率,Jlink Pro不限制采样率,不过用Jlink Pro采样率设高了,Ozone的Timeline波形刷新很卡,所以用VOFA+来采集高速变量数据并显示波形,采样率与PWM频率同频16k。USB串口设为10M的波特率会有点问题,接收的数据乱码,最终通信波特率设为8M。8000000/16000/10/4=12.5,采用DMA理论上一个PWM波周期串口可以发送12.5个4字节变量数据,考虑一定的时间余量,本次测试发送11个浮点数据,包括10个变量数据和1个帧尾数据。以下是测试结果:

(1)、测试现场

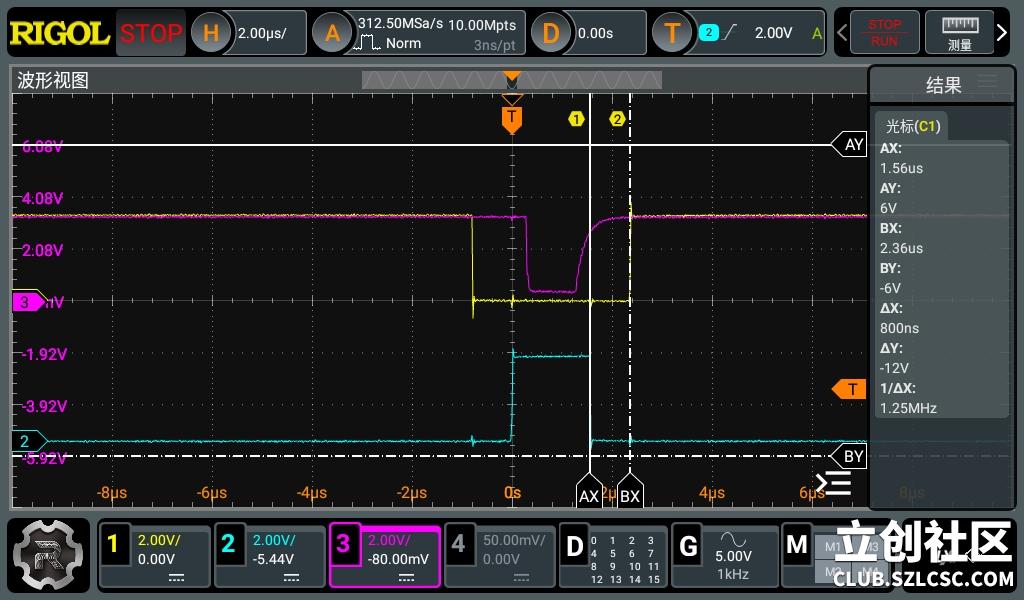

注:黄色是U相上桥PWM波,青色是U相下桥PWM波

注:黑色小板为高速USB转TTL串口,最高支持12M的波特率。

(2)测试波形图

注:Ozone调试界面

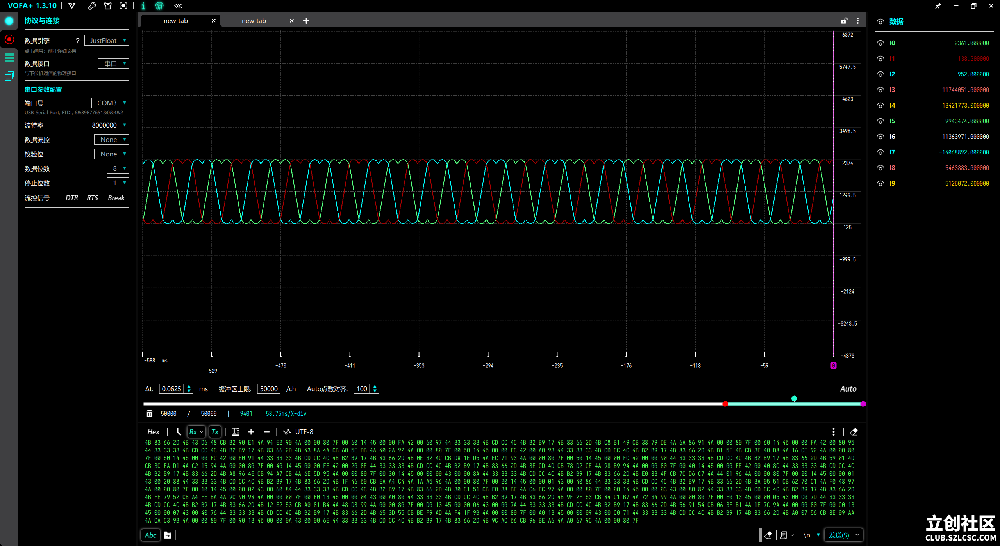

注:给定Vd = 0,Vq为0.5*2^24=8388608,SVPWM马鞍波形,周期为50ms,即20Hz。VOFA+上位机波形显示与程序设定一致。

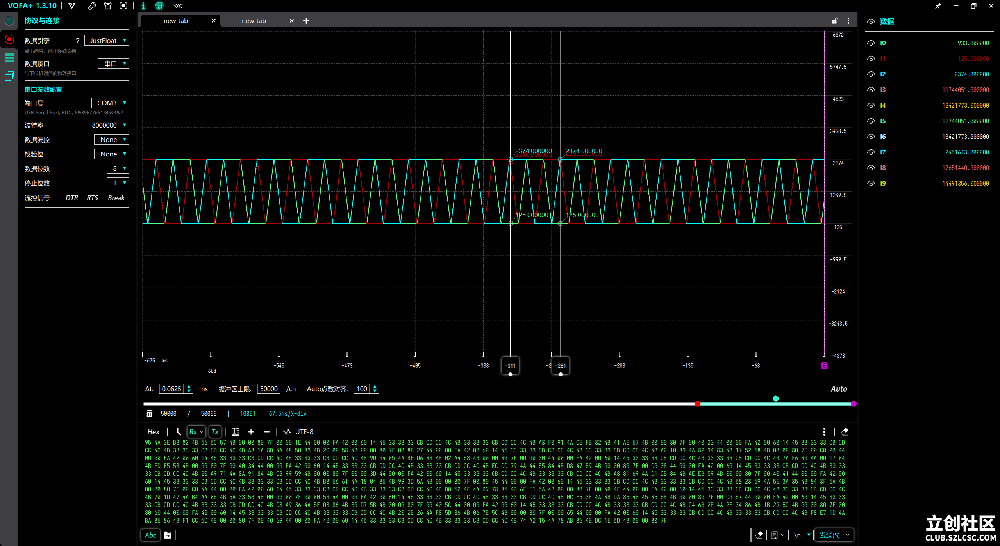

注:当sqrt(Vd^2+Vq^2)>0.9时。电压极限圆将最大最小占空比限制在0.95及0.05(PWM波周期寄存器值为2500)。

注:以上波形为电压极限圆输入的Vd、Vq,以及输出Vd_limit、Vq_limit。反park变换后的Ualpha、Ubeta。开环角度Angle。

注:以上波形关闭电压极限圆限制后,SVPWM输出的占空比波形不再时马鞍形状。

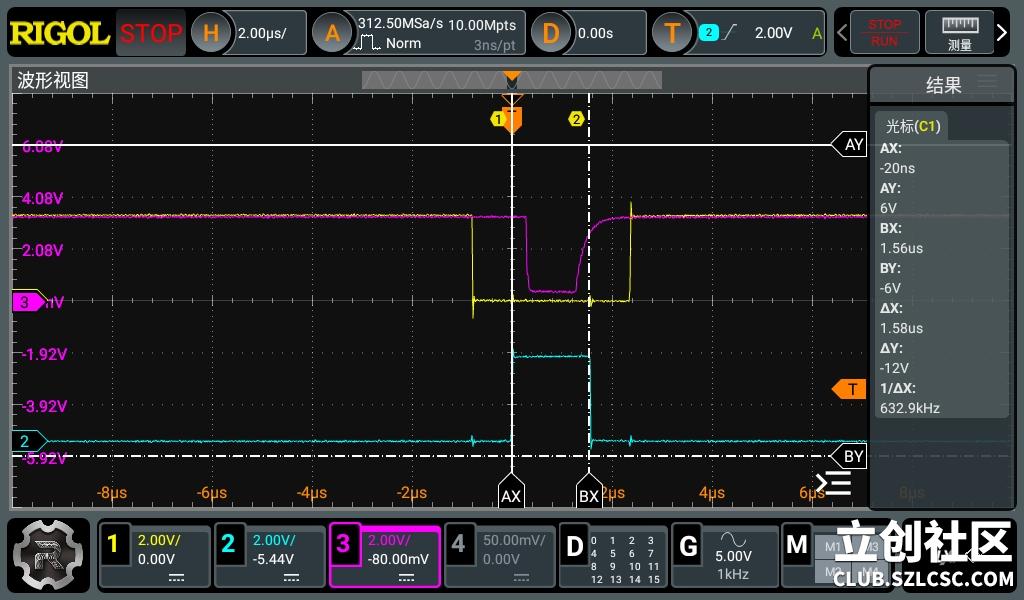

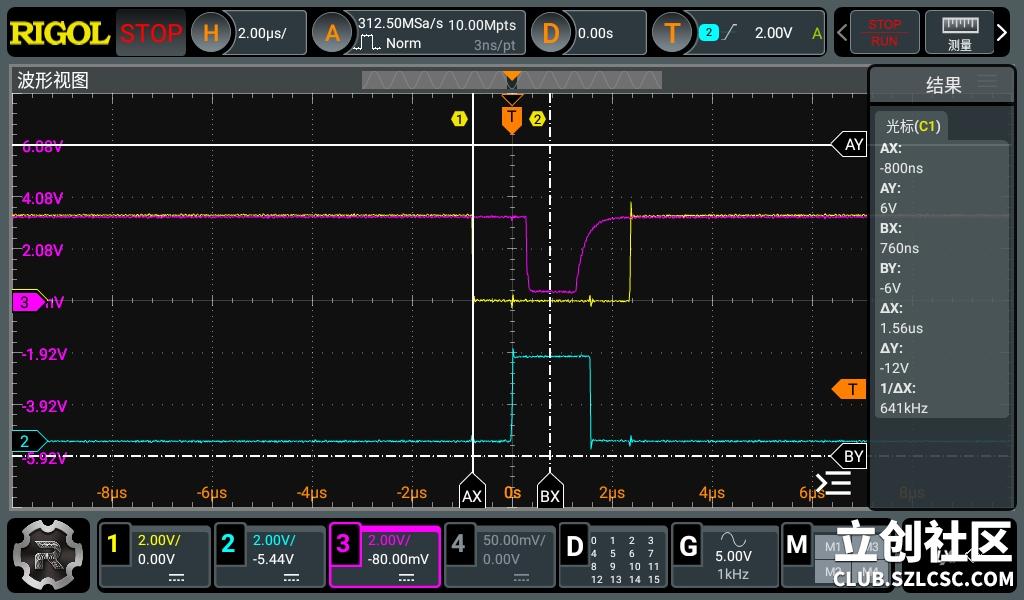

注:以上波形中,紫色为触发ADC采样信号,黄色为U相上桥PWM波,青色为U相下桥PWM波形,从图上可以看出,死区的插入都是在下桥完成,SysConfig软件中配置的死区为前后都是800ns,ADC出发时采样点为40即500ns位置(PWM波时钟频率80M)。死区插入后,下桥延时800ns导通,提前800ns关断。当最小占空比为0.05时,理论比较点为0.05*2500=125,125/80000000=1.5625us,理论上没有死区时,下桥导通时间应该为1.5625*2=3.125us,加入死区后实际下桥导通为1.56us,3.125us-0.8us-0.8us=1.525us,与实际波形相符,验证分析正确。以前接触到的死区插入方式都是上下桥上升沿延时一定时间。这样的死区插入方式会影响到相电流采样时间,下桥导通时间过短,可能会造成相电流采样不准确。死区配置是参考了Ti的无感Foc例程里面的配置的,不知道是不是跟SysConfig软件配置死区的模式有关,这个问题有待后续验证。

附件: |

立创商城小编

立创商城小编

222

主题

152

回复 |

4#

恭喜您入选本次测评活动前三名,我们将在2月2日前,派发以下奖励至你的客编。 奖励1:立创采购晶50 奖励2:立创商城满101减100优惠券,有效期30天。 请记得及时使用优惠券,祝您工作顺利! |

|

发表于2024-01-19 10:39:12

发表于2024-01-19 10:39:12

收藏

收藏