|

查看:

16551

回复: 22 |

试用2天EDA,问题

|

|||

致新科技工程师

5

主题

12

回复 |

1#

电梯直达

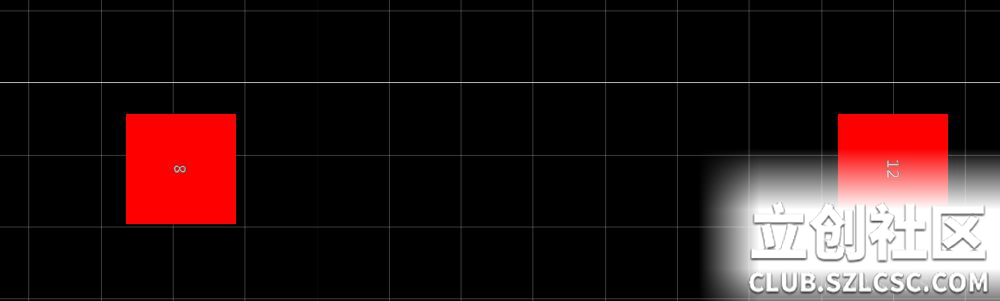

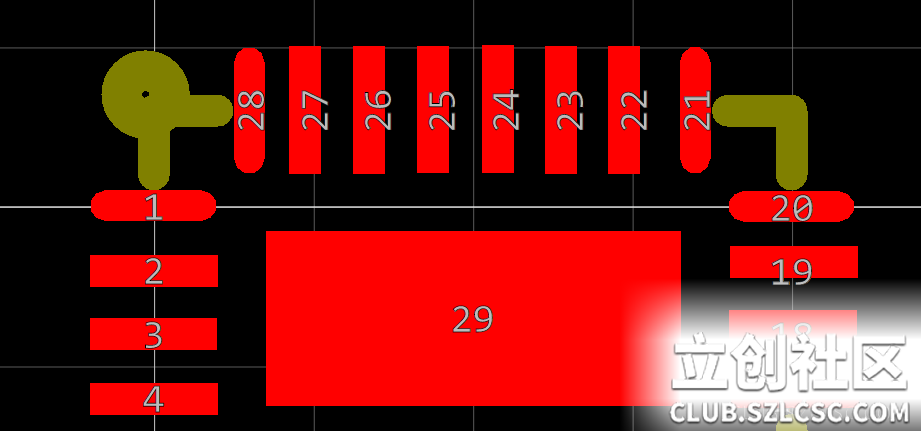

1. PCB封装设计时,焊盘的对齐有问题。网格大小为1mm,栅格尺寸0.1mm,ALT键栅格0.1mm.采用吸附。下图的PIN4和 PIN17的垂直坐标都是1.2mm,但从图像看,怎么都不整齐。这是什么原因呢? 2. PCB 覆铜极度不方便,使用实心填充,就没办法区分网络。使用覆铜的方式,那个边框好讨厌。如果在同一层要覆铜好几个网络的话,就麻烦了。 3. 画实心填充和覆铜时,无法设置光标的最小行程。无发固定45度转角等。 4. PCB时光标的最小行程要能设置,才好LAYOUT。每次覆铜时画错一点,都要重来。

GMT-Billy

|

|||

立创EDA罗工

立创EDA罗工

78

主题

4623

回复 |

3#

跟据你的参数我这里是平的,你的操作步骤是怎么样的?

技术支持微信:请前往lceda.cn获取二维码,官方群:不再提供QQ群,公众号:立创EDA 或 开源硬件平台

|

|||

立创EDA罗工

立创EDA罗工

78

主题

4623

回复 |

4#

铺铜以后可以编辑每一个端点的坐标。

技术支持微信:请前往lceda.cn获取二维码,官方群:不再提供QQ群,公众号:立创EDA 或 开源硬件平台

|

|||

立创EDA罗工

立创EDA罗工

78

主题

4623

回复 |

5#

光标行程需要设置snap size

技术支持微信:请前往lceda.cn获取二维码,官方群:不再提供QQ群,公众号:立创EDA 或 开源硬件平台

|

|||

立创EDA罗工

立创EDA罗工

78

主题

4623

回复 |

6#

已邮件回复你。

我这边使用Chrome和Firefox是正常的,请问你是否使用其他浏览器?比如IE或者Edge。

我们只支持Chrome和Firefox,其他的没有做适配兼容,所以建议你使用Chrome和Firefox访问Web版EDA,或者使用客户端。

客户端下载地址:https://lced

技术支持微信:请前往lceda.cn获取二维码,官方群:不再提供QQ群,公众号:立创EDA 或 开源硬件平台

|

|||

立创EDA罗工

立创EDA罗工

78

主题

4623

回复 |

8#

栅格就是了

技术支持微信:请前往lceda.cn获取二维码,官方群:不再提供QQ群,公众号:立创EDA 或 开源硬件平台

|

|||

立创EDA罗工

立创EDA罗工

78

主题

4623

回复 |

11#

收到,我找一下

技术支持微信:请前往lceda.cn获取二维码,官方群:不再提供QQ群,公众号:立创EDA 或 开源硬件平台

|

|||

立创EDA罗工

立创EDA罗工

78

主题

4623

回复 |

16#

比如说哪些地方不够人性化不方便?

技术支持微信:请前往lceda.cn获取二维码,官方群:不再提供QQ群,公众号:立创EDA 或 开源硬件平台

|

|||

立创EDA罗工

立创EDA罗工

78

主题

4623

回复 |

18#

这些都还没有开始做。。。。 大神,可以做一份你觉得哪些地方需要改善的汇总么,我们也好参考是否可以做,或者我们已经有记录还没有开始做也不一定。谢谢

技术支持微信:请前往lceda.cn获取二维码,官方群:不再提供QQ群,公众号:立创EDA 或 开源硬件平台

|

|||

立创EDA罗工

立创EDA罗工

78

主题

4623

回复 |

20#

这个很快就可以改善了

技术支持微信:请前往lceda.cn获取二维码,官方群:不再提供QQ群,公众号:立创EDA 或 开源硬件平台

|

|

发表于2017-08-12 11:47:54

发表于2017-08-12 11:47:54

收藏

收藏