|

查看:

186684

回复: 69 |

嘉立创阻抗多层板:层压结构及参数

|

||||||||||||||

|

1#

电梯直达

嘉立创阻抗多层板:层压结构及参数前言:嘉立创因客户的强烈需求自2018年增加了层压结构及公布出来,极大的方便广大客户按嘉立创的层压结构及相关参数进行阻抗匹配设计,在下单系统中,将支持下面的层压结构,生产将严格按下列的层压结构进行生产,相关的层压结构嘉立创都生产了阻抗测试条进行了测试! 测试条现场测试的图片:http://club.szlcsc.com/article/details_11485_1_22.html#floor_22

一:阻抗设计相关参数: PP介电常数:

二:算阻抗的阻焊油相关常数

一:四层板阻抗层压结构一:成品板厚:0.8MM 1) JLC7628结构:

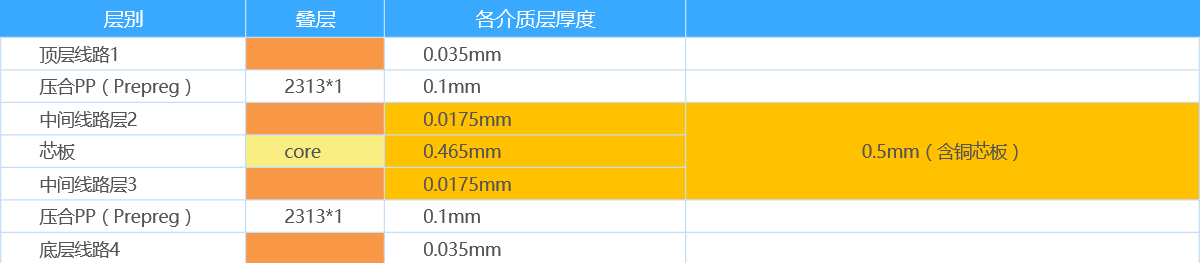

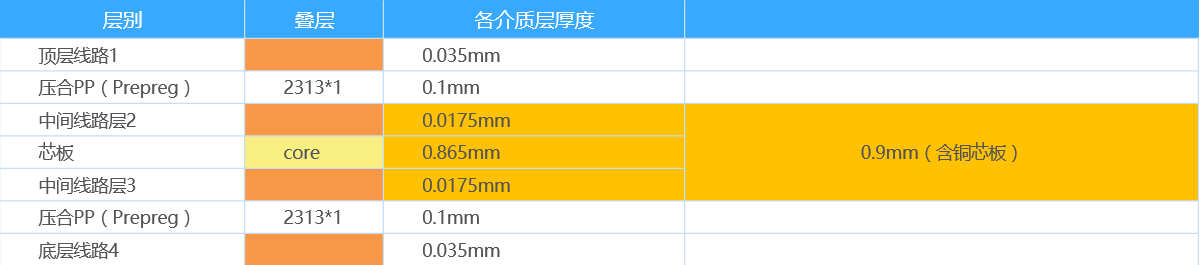

2) JLC2313结构:

二:成品板厚:1.0MM 1) JLC7628结构:

2) JLC2313结构:

三:成品板厚:1.2MM 1) JLC7628结构:

2) JLC2313结构:

四:成品板厚:1.6MM 1) JLC7628结构:

2) JLC2313结构:

五:成品板厚:2.0MM 1) JLC7628结构:

注:2.0板厚四层板只提供一种层压结构 二:六层板阻抗层压结构一:成品板厚:1.2MM

二:成品板厚:1.6MM

三:成品板厚:2.0MM

注:6层板暂时只提供一种层压结构

深圳嘉立创科技发展有限公司 WWW.SZ-JLC.COM 2018年3月1日星期四 |

||||||||||||||

|

2#

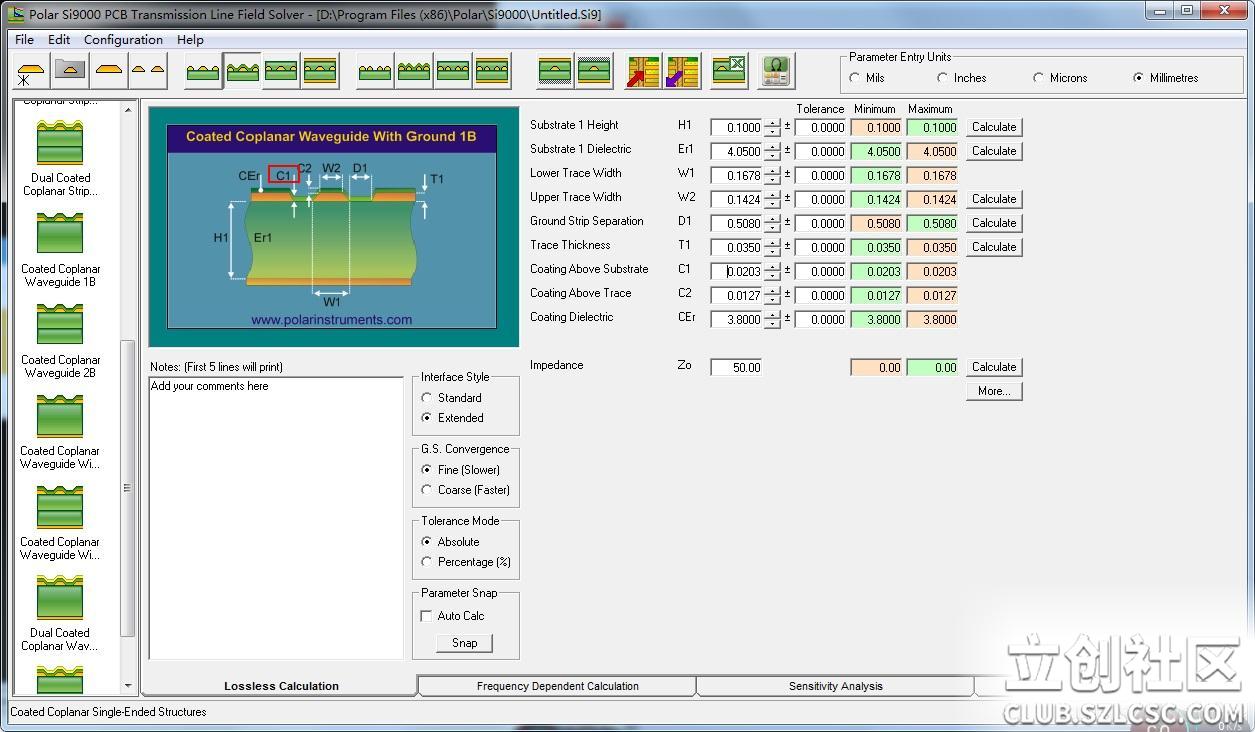

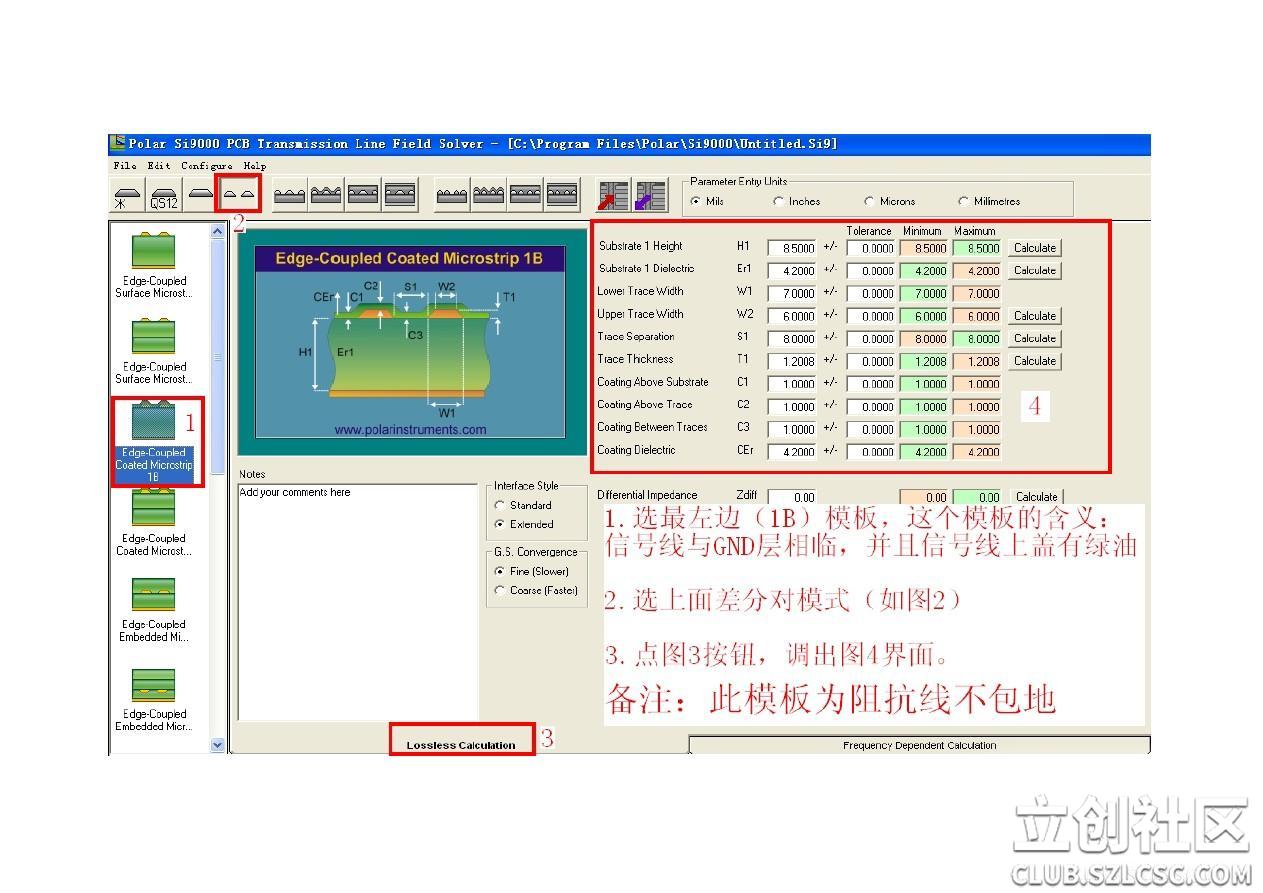

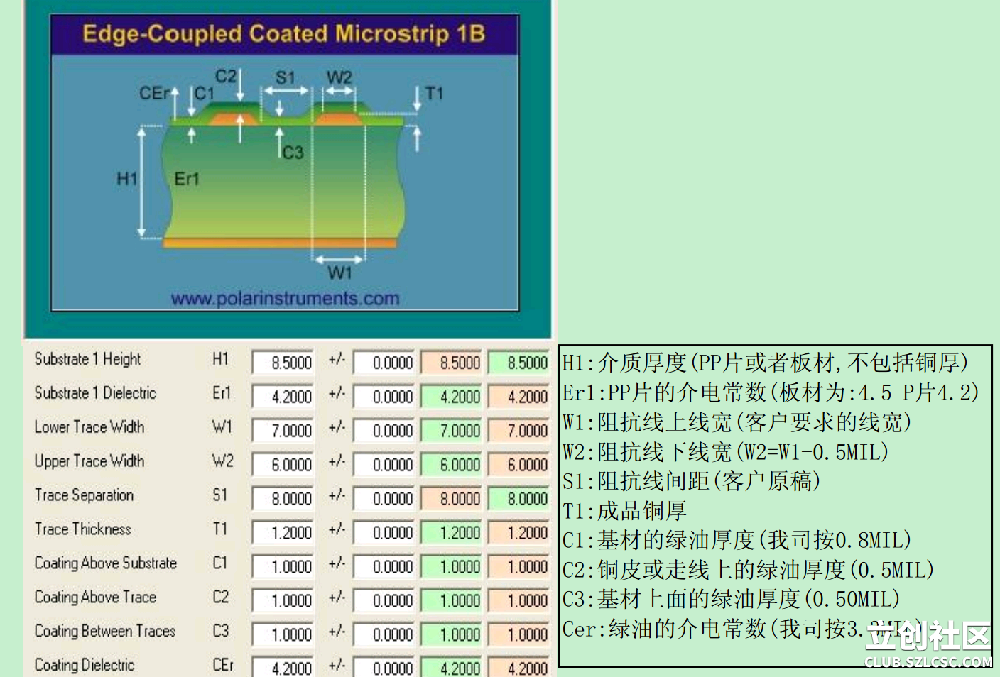

顺便上一个阻抗计算工具示例,让大家自己计算好线宽线距,安排好叠层

|

||||||||||||||

|

3#

以经在开发

|

||||||||||||||

|

4#

我也好想知道,贵公司的阻抗软件什么时侯能上线。便于我们设计。呵呵,等待中。。。。。 |

||||||||||||||

|

5#

阻抗计算工具,等待中。。。。。

|

||||||||||||||

|

6#

阻抗计算工具可以用SI9000

|

||||||||||||||

|

7#

期待

|

||||||||||||||

|

8#

7628, 2313都已经投产了?

|

||||||||||||||

|

9#

投产了

|

||||||||||||||

|

10#

帅!终于有了!

|

||||||||||||||

|

11#

请问一下,这两种结构有它们优劣点和不同点吗?我们要用设计阻抗匹配在哪种情况下用哪种结构会好点?

|

||||||||||||||

|

12#

你好,版主: 我没有软件,我打算按你们提供的6层板叠层结构布线,有3对差分走线,我要走11mil线宽,线距8的情况下,默认这个叠层是多少阻抗的呢?我预期要90欧的! |

||||||||||||||

|

13#

你好,管理员,需要您帮忙确认一个问题,如图 ,图中的差分线间距(S1)是中心间距还是线的边缘间距呢?请请教!

|

||||||||||||||

|

14#

cool !

|

||||||||||||||

|

15#

芯板的介电常数哪位知道?

|

||||||||||||||

|

16#

什么时间可以做半孔工艺?等......... |

||||||||||||||

|

17#

双层板的阻抗匹配什么时候可以呢?

|

||||||||||||||

|

18#

什么时候支持0.6mm的板子啊

|

||||||||||||||

|

19#

设计电路的时候,比如说出gerber的时候,阻抗信号的线宽给的是W1还是W2啊,1oz的w1和w2我选取1mil的差别合适不合适? |

||||||||||||||

|

20#

请问上述材料的介电常数是在信号频率是多少的时候的数值?

|

||||||||||||||

|

21#

上两个50欧阻抗微带线计算结果供参考。四层板,表层走线(相邻中间板层为电源地)微带线安全距20mil 1) JLC7628结构:

2) JLC2313结构:

6层板的表层微带线 也可以参考2313结构。注意相邻板层必须是电源地。 |

||||||||||||||

|

22#

感谢分享。

|

||||||||||||||

|

23#

嘉立创的一般两层板的叠层有没有? 介电系数多少?之前按照4.6来算,有偏差。

|

||||||||||||||

|

24#

这个应该是指线的边缘之间的距离。

|

||||||||||||||

|

25#

既然有了叠层,jlc应该提供一组参考值。

|

||||||||||||||

|

26#

芯板的介电常数没有提供哦,如果设计板子是1.2mm 的6层板,叠层按SGGSGS设计,那么L4层如果走阻抗线就属于带状线,要使用Si9000的Edge-coupled Offset stripline 1B1A 模型进行设计,需要输入PP和core的介电常数进行计算,帖子里只给出了PP的,那0.4mm含铜芯板的介电常数呢?

|

||||||||||||||

|

27#

黑色批量4层板,什么时候能做第二种层压的

|

||||||||||||||

|

28#

我想问一下,投板时在哪里选择上面的结构呢?

|

||||||||||||||

|

29#

请问是选择了厚度就等于选择了叠层结构吗?可以每种厚度有有两种JLC7628和JLC2313。这个怎么指定呀?

|

||||||||||||||

|

30#

下单时有选择

|

||||||||||||||

|

31#

请问7628板材是什么颜色的?

|

||||||||||||||

|

32#

一年了,还在等待阻抗计算工具中。。。。。。

|

||||||||||||||

|

33#

早就推出了

|

||||||||||||||

|

34#

注意到上面几位朋友用Si9000仿真差分阻抗的时候,W1和W2选择不同的值。我不太明白,假如Allegro里面按照线宽6mil走线,那么我仿真的时候,W1和W2分别应该填多少?谢谢!

|

||||||||||||||

|

35#

阻抗计算工具

|

||||||||||||||

|

36#

相差1mil

|

||||||||||||||

|

37#

为什么黑色板子不能选择2312结构……

|

||||||||||||||

|

38#

双层板的介电常数是多少?

|

||||||||||||||

|

39#

后续会添加阻抗测试吗?这样看到才能知道打出来的板阻抗对不对。

|

||||||||||||||

|

40#

不存在优劣,不同的板厚,你会有不同的设计线宽,这里只有0.1 和0.2mm 两种厚度,可选择的太少了,通用性不够。

|

||||||||||||||

|

41#

嘉立创阻抗神器 计算后 给出的线宽是上线宽(W2 ) 还是下线宽(W1)

|

||||||||||||||

|

42#

兄弟,这里没有人回答问题的,只有人问问题..................

|

||||||||||||||

|

43#

|

||||||||||||||

|

44#

多谢多谢!!!!

|

||||||||||||||

|

45#

请问core的介电常数是多少。

|

||||||||||||||

|

46#

你们阻抗匹配不需要输入频率吗 |

||||||||||||||

|

47#

为什么一楼还有阻焊油的介电常数和厚度数值?第一次见,算阻抗要算到这么令人发指的精确吗?

|

||||||||||||||

|

48#

请教楼主一个问题。 根据贵司的6层板叠层设计,top和第二层之间是0.1mm,压合PP材料2313的介电常数是4.05,我用网上的阻抗计算器算了一下: https://www.eeweb.com/tools/microstrip-impedance Trace Thickness 0.035mm Substrate Height 0.1mm Trace Width 0.1mm (4 mil) Substrate Dielectric 4.05 得到的Impedance是66.2 Ohms。如果线宽调整为0.15mm(6 mil),得到54.9 Ohms。如果线宽调整为0.18mm(7 mil),可以得到49.8 Ohms。 通常大家是需要50 Ohms阻抗的;对于DDR3,一些芯片可以宽泛到50-75 Ohms,一些推荐在55 Ohms +/- 10%,但大部分严格一些的是要求50 Ohms。很显然对DDR3这样的走线,6mil/7mil都不大可能,请问你们的建议是什么?我看到的一些参考设计都相应的降低了PP层的厚度。 |

||||||||||||||

|

49#

2313组矿版如何下单? |

||||||||||||||

|

50#

没有8层板及以上的层压结构吗?

|

||||||||||||||

|

51#

下面的线宽,界面呈梯形,上面比小面少0.5mil

|

|

发表于2018-03-02 09:59:36

发表于2018-03-02 09:59:36

收藏

收藏