|

查看:

1291

|

回复:

0

|

从三个层面认识SRAM存储器

|

是酒窝啊

196

主题

231

回复 |

1#

电梯直达

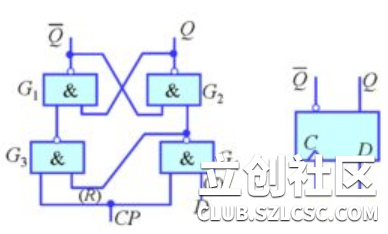

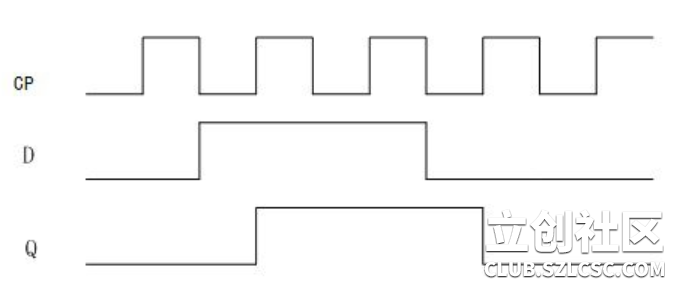

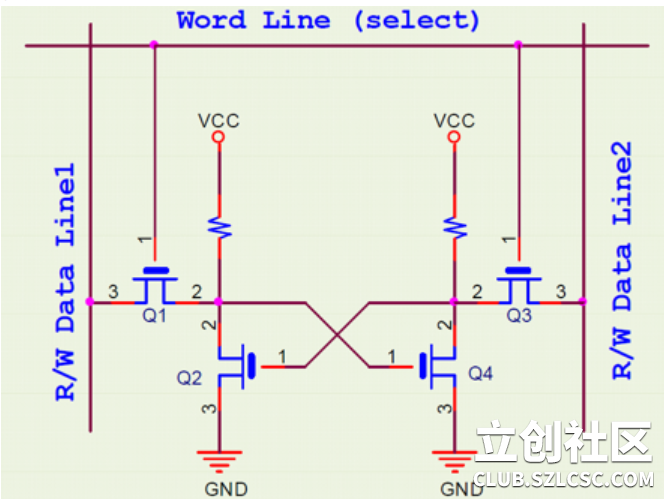

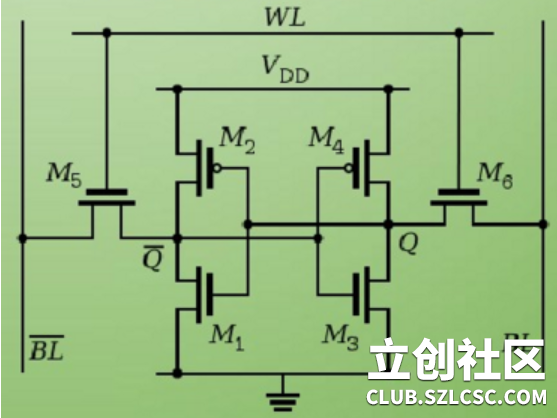

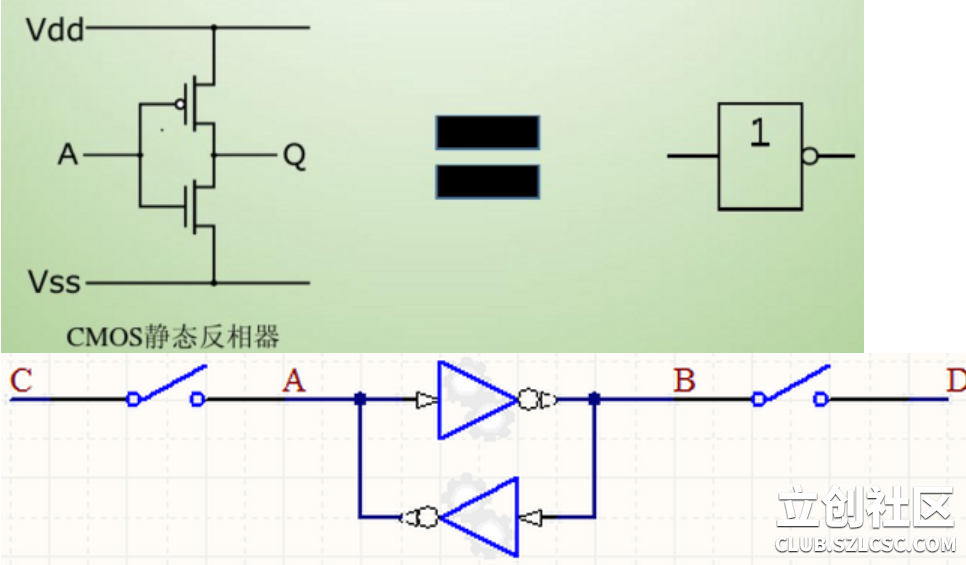

大家都了解,CPU是负责计算和处理的,而存储器则是负责互换数据信息的。有些人是那么形容的,说CPU便是技术工程师自己,运行内存就好像操作台,必须妥善处理的物品必须先取得工作中台子上才便捷解决。那么硬盘是什么呢?电脑硬盘如同木柜,储放电子元器件仪器设备用的库房,存物品。下面专注于代理销售SRAM、MRAM、Flash等存储芯片供应商宇芯电子从三个层次介绍SRAM。 存储器有两个基础的组成模块,充足了解SRAM和DRAM这两个定义及其电路原理,针对学习工具CPU架构及其DDR十分有效。DRAM便是动态随机存储器,SRAM是静态数据随机存储器。这一动一静的实质是什么呢?先说静态数据随机存储器,它是运用如D触发器的构造来进行数据信息的载入与载入的,材料的载入不用刷新动作,那样不用更新动作的就变成静态数据。那样促使控制系统设计非常简单,存储的速率比DRAM快许多。适用于于髙速储存的应用领域例如CPU的cache缓存文件。 了解完静态数据随机存储器以后,动态性随机存储器就比较好了解。动态性是指运用电容器的蓄电池充电来完成材料的载入与载入姿势,由于电容器会渐渐地充放电,假如充放电到阀值下列,数据信息很有可能便会遗失了,因而必须每过一段时间来做更新的姿势,以维持材料的一致性。最普遍的便是手机上和电脑上的运行内存了。 1、第一层了解—一个D触发器组成非常简单SRAM首先从最基本数字电路设计开始。有一个很基础且深刻的认识:SRAM cell最简单的构成单元就是一个D触发器,如下图所显示的D触发器是数字电路设计系统软件里边的一个基础模块。 1bit的SRAM模块的关键电源电路便是一个D触发器。当有power存有的情况下,由于D触发器的特点,数据信息能够储存,不用刷新。触发器原理是具备记忆力作用的,具备2个平稳的信息内容存储状态。D触发器的特点方程组是:Q(n+1)=D;也就是记忆力前一个情况,能够从RS触发器考虑,写一下真值表,测算就很好了解了。 2、第二层了解—4个多管组成的SRAM随后,可以用基础晶体三极管方面来构建一个简易的SRAM模块,只是由4个NMOS管和2个电阻器组成的。 3、第三层了解--6管多管组成的SRAM最终,能够从IC的生产制造方面看来。实际上绝大多数与第二层类似,仅仅M2与M4用PMOS替代。SRAM中的每一bit储存在由四个场效管(M1,M2,M3,M4)组成2个交叉耦合的反相器中。此外2个场效管(M5,M6)是储存基础模块到用以读写能力基准线(BitLine)的自动开关。 一个SRAM基础模块有0和12个脉冲信号平稳情况。SRAM基础模块由2个CMOS反相器构成。2个反相器的键入、輸出交叉式联接,即第一个反相器的輸出联接第二个反相器的键入,第二个反相器的輸出联接第一个反相器的键入。这就能完成2个反相器的輸出情况的锁住、储存,即储存了一个位元的情况。

宇芯电子主要产品线有静态随机存储器SRAM,非易发性存储器MRAM,伪静态存储器PSRAM等多种类型随机记忆体及微控制器MCU等半导体产品,189-2655-4009

|

|

发表于2020-09-01 15:59:23

发表于2020-09-01 15:59:23

收藏

收藏