|

查看:

19788

回复: 17 |

嘉立创高难度多层板的层压结构,对有阻抗要求的有帮助...

|

|||

limeng

limeng

【官方工作人员】

188

主题

797

回复 |

1#

电梯直达

1)能提供给线宽/线隙 3.5mil 最小过孔0.2mm 最小BGA:0.25mm 的工艺参数,而价格能做到普通工艺参数价格一样的目前宇宙内找不到几家,四层板最低价格仅收(5X5CM以内打样10片) 100元 (10cmx10cm以内打样10pcs打样10PCS)仅收200元,多层板样板也快速增涨了50%!  各家的参数,只要是玻纤板FR-4,都是差不多的!

深圳市嘉立创科技发展有限公司

PCB事业部:http://www.sz-jlc.com QQ:3001295068

|

|||

John

6

主题

276

回复 |

2#

绿油的介电常数也应该给出来,记得好象是3.26

HiFi用三端稳压器安森美LM337BTG,超低Ciss 1400pF NMOS管安森美NTMFS5C670NLT1G

|

|||

Mosman

7

主题

75

回复 |

3#

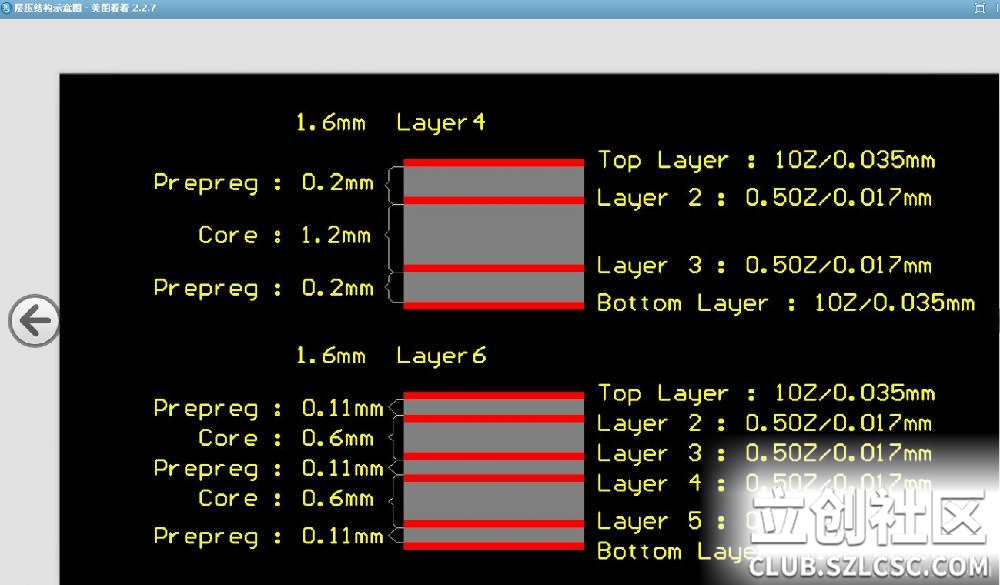

让我郁闷的是为什么4层板的Prepreg不用0.11mm厚的,这样最适合50ohm的阻抗线。

* 0.11mm厚度走50ohm的阻抗线的线宽是6mil,正好合适设计; 0.2mm厚度走50ohm的阻抗线的线宽是13mil,偏宽,不适合设计。

早在3年前就提出这样的要求,JLC回复不支持。

|

|||

9999jim

0

主题

3

回复 |

4#

|

|||

limeng

limeng

【官方工作人员】

188

主题

797

回复 |

5#

能加我QQ么,讨论一下745434669

深圳市嘉立创科技发展有限公司

PCB事业部:http://www.sz-jlc.com QQ:3001295068

|

|||

Mosman

7

主题

75

回复 |

6#

你可以电话联系我

|

|||

BlackDove

1

主题

14

回复 |

7#

高精度板是有阻抗要求,0.2是不太好搞。 如果0.2和0.11有差价,那可以让客户选择,加费用呗。

|

|||

redleaves

4

主题

93

回复 |

8#

做6层不就得了,既然不差钱。

|

|||

BlackDove

1

主题

14

回复 |

9#

这话说得就没道理了,只是合理化建议,没必要阴阳怪气。 6层和4的差价一倍都不止, 换0.11的能有多大差价?

|

|||

GUO

GUO

【官方工作人员】

24

主题

193

回复 |

10#

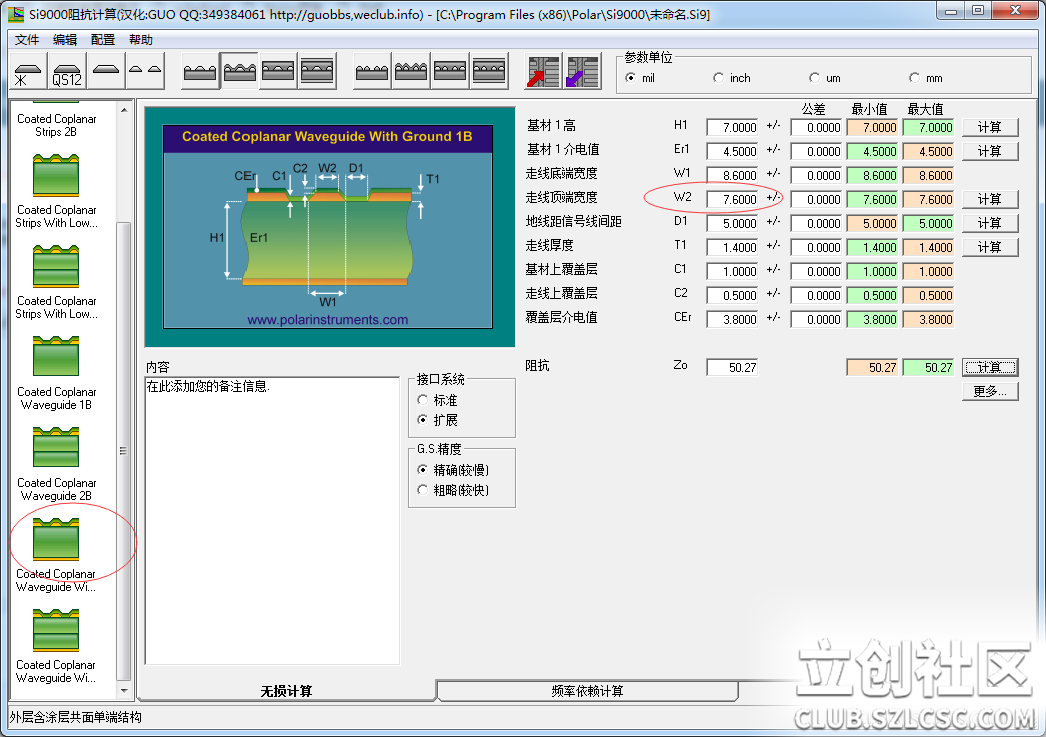

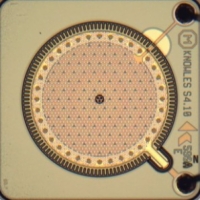

可以设计成 7.6mil 根JLC给出的叠层参数 , 为了满足50ohm的单端阻抗, 走线要尽可能的小, 要采用共面单端阻抗模型来设电路, 线宽设计为7.6mil即可满足50ohm, 如下图所示效果 备注: H1是指PP, 7628的PP出厂厚度一般是8mil, 压合后实际厚度一般在 7 mil的样子, 这个厚度值是受流胶和内层线路铜面积的影响, 铜面积越低实际H1的厚度就越偏薄, 为什么呢, 这是因为PP中的含胶有一部用来填充内层线路间的间隙了. D1是指阻抗线距周边大铜皮的间距<这就是所谓的共面>, 这个值对阻抗有影响, 它同阻抗值成正比, 建议不要低于5mil, 因为它旁边是大铜皮, 这个值太小, 在PCB制造工艺中容易引起电镀夹膜.

|

|||

Mosman

7

主题

75

回复 |

11#

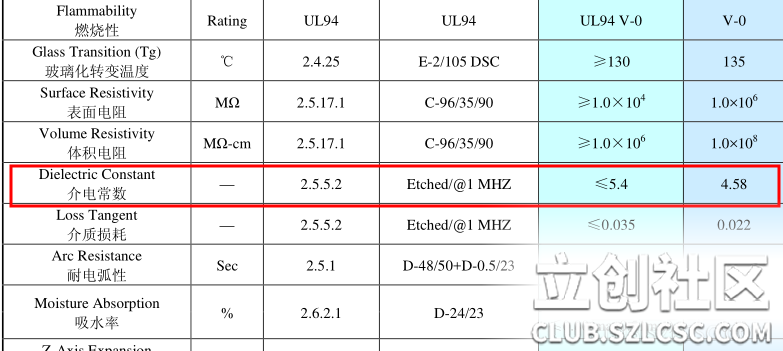

介电常数不能按照4.5算,4.5是100MHz的介电常数, 高速电路里面一般都是按照1GHz的介电常数来计算的。

|

|||

GUO

GUO

【官方工作人员】

24

主题

193

回复 |

12#

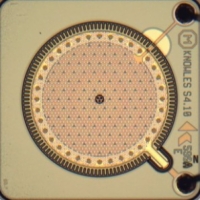

主要看PP片的厂家给的参数, 上面给的介电常数是低于5.4, 常用值4.58, 我选4.5是没有问题的, 你也可以改成4.58 事实上不同厂家, 不同厚度的PP的介电常数并不是固定的, 建滔我使用的少, 之前用的生益的比较多 7628的PP介电常数一般是大于: 4.2 2116: 3.8左右 3313: 3.7左右 1080: 3.5左右 我记的也不是太准了, 准确的值以PP的厂家参数为准, 如上图所示. |

|||

Wattle0Hua

6

主题

110

回复 |

13#

请问一下,介电常数有1GHz的么?

|

|||

Wattle0Hua

6

主题

110

回复 |

14#

一大把数字走线的时候走不成这样的…… 小功率射频的可以这样做

|

|||

GUO

GUO

【官方工作人员】

24

主题

193

回复 |

15#

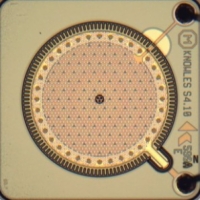

介电常数就是那样,常规FR4的板子,阻抗就是这样算的, 达不到产品需求, 只能通过其它的方式来解决. 用1.0的开料板厚+2张7628的PP来做四层板, 是PCB厂家最喜欢采用的结构, 量大工艺稳定. 当然为了满足单端阻抗的设计采用 1.2板厚+2张2116的PP, 也是问题不大的, 这个要看这类需求有多少. 特殊板子, 比如通讯基站用的高频板, 介电常数最低的一般是高频板材PTFE<俗名铁氟龙>, 介电常数只有 2.x 这板子不好做, 生产流程更复杂, 价格也非常壕. 罗杰斯的陶瓷板介电常数也不高 3.x |

|||

云淡风清

1

主题

30

回复 |

16#

1.0板厚的层压结构呢?

|

|||

a258684

1

主题

1

回复 |

17#

我还是喜欢0.2mm厚度,因为做射频电路线太细损耗太大

|

|||

精确精密精妙

11

主题

14

回复 |

18#

这个不错,早就想问,找不着问的地方

|

|

发表于2017-12-05 18:06:16

发表于2017-12-05 18:06:16

收藏

收藏