|

查看:

84487

回复: 44 |

嘉立创叠层结构之阻抗设计技术分享

|

|||

GUO

GUO

【官方工作人员】

24

主题

193

回复 |

1#

电梯直达

2018新年过罢, 嘉立创正式推出标准化多层板的叠层结构, 四层板新增了一种叠层结构, 老司机朋友们都知道叠层结构的丰富给客户layout画板的发挥空间更大, 比如有特性阻抗需求的板子, 高频线路等, 这对多层板客户来说绝对是一大福利. 怎么样好好利用这些叠层结构? 其实一般的板子用什么结构都是无所谓, 主要是有阻抗需求的板子选用什么叠层结构是需要花费一些心思的. 以1.6mm的成品板厚为例来看一下更新后的各叠层结构<其它厚度基本上都是芯板的厚度变化, PP结构是不变的, 除了2.0mm的6层板中间是使用的7628的PP>.

从上面图中可以看出,提供了详细的数据,计算阻抗需要的数据基本上都有了. 很多小白, 就是卡在怎么模拟计算阻抗上面来的. 模拟计算阻抗一般是使用一款名为Si9000的软件来计算, 这是由Palor公司出品的软件, PCB行业基本上都是使用这款软件计算阻抗. 这是一款收费软件,请购买正版软件 先介绍一下这款软件的基本界面 图片太大不介绍了

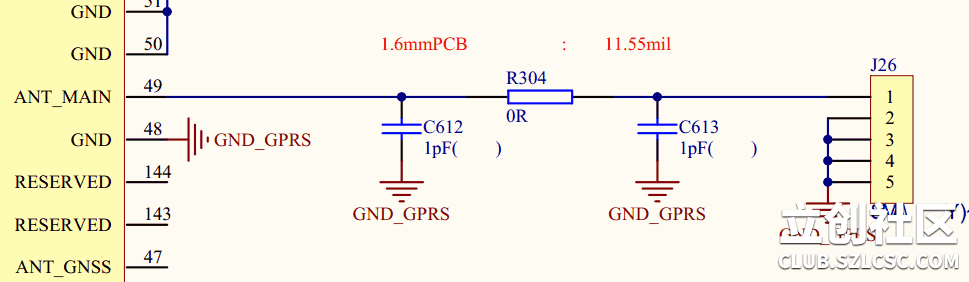

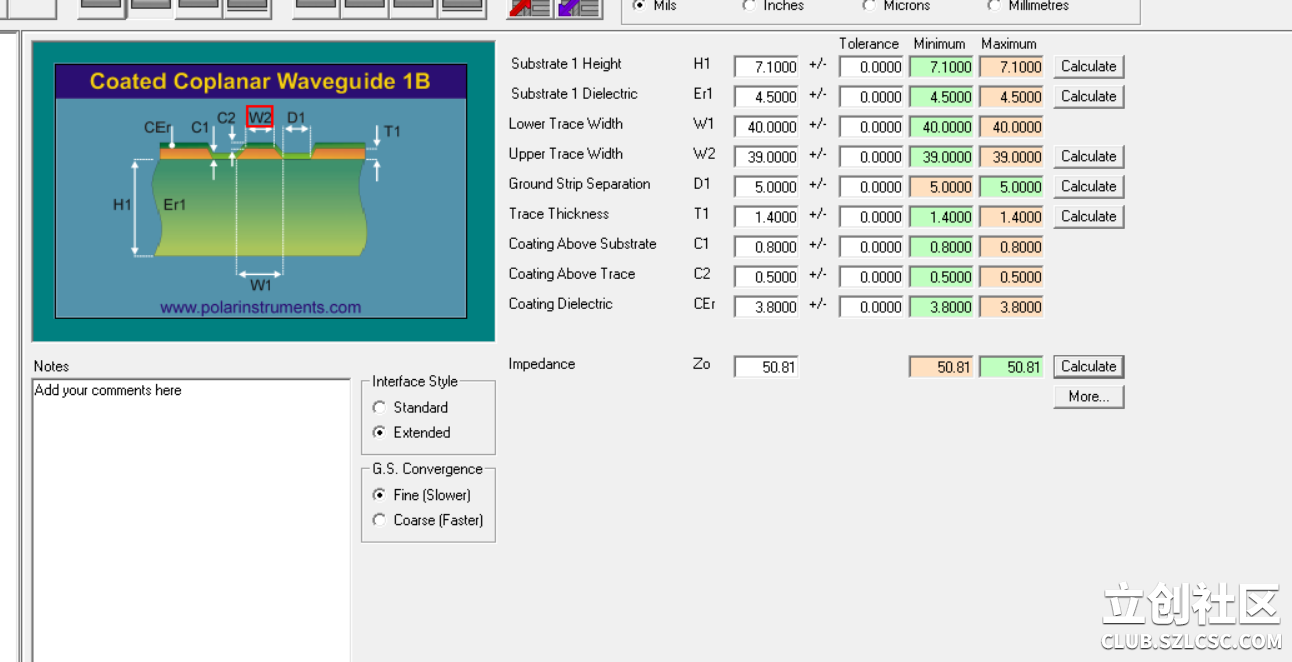

案例一: 嘉立创7628结构, 4层板, 1.6板厚, 外层50ohm的单端阻抗, 线宽该设计多宽? 首先要找到正确的计算模型, 首选下图所示的模型: 模拟计算效果图, 如下图, W1表示我们要设计的阻抗线的走线宽度, 各参数一一说明: H1: 表示7628PP的成品厚度, 低含胶量7628PP的出厂厚度是7.6mil, 压合时有流胶损耗, 所以统一按7.1取值, 这是一个约等于值不用太较真. Er1: PP的介电常数 W1: 成品线宽, 也就是我们的画图设计走线宽度 W2: 走线顶端宽度, 表示侧蚀的意思, 外层成品1oz的铜厚一般按1mil的侧蚀量计算. T1: 表示成品铜厚 C1: 基材上的阻焊厚度 C2: 走线面上的阻焊厚度 CEr: 阻焊的介电常数 Zo: 当然是指阻抗值了 计算技巧: 1): 有"计算"按钮的都可以计算对应的值, 比如其它参数输入好后, 可以计算这个要求的值, 在嘉立创固定叠层结构的情况下, 我们参使用的计算按钮不多, 只有阻抗和线宽互相推算, 其它值基本上都是确定的, 我们可以根据指定的阻抗值推算走线宽度, 相反根据阻抗宽度推算阻抗值. 走线宽度一般都是取整设计, 比如 4.0mil, 4.5mil, 5.0mil, 5.5mil, 6.0mil ........, 像这样子的, 我一般是先输入要求的阻抗值, 反推走线宽度, 然后再将宽度值按最近原则取整, 如下图的效果得出来的阻抗值是50.6ohm, 但是这没有什么问题. 走线宽度不取整也行, 但以mil为单位保留小数点后1位即可. 2): 看图中"最小值","最大值"两列是有颜色的, 这个颜色是有讲究的, 颜色方向一致的, 表示成正比, 方向相反的表示成反比. 什么意思呢? 下图W和Zo的方向是反的, 说明两都成反比, 就是走线越宽阻抗就越小, 反之走线越细阻抗值就越大, 这个在后面计算差分阻抗线调整线宽线距很有用. 设计技巧: 下图中的H1是7.1mil, 说明线路下面对应的参考层铜箔实际上是第2层线路, 如果你的参考层是第三层线路或者第四层线路, 那么H1的值就不是7.1mil了, 而是外层线路到参考层间的所有介质的总厚度, 介电常数一般是取最高的那一个即可(事实上多介质混合介电常数有更精细的计算公式, 这里就不过多介绍了). 这个参考层很重要, 这些计算模型实隙上就是你的板子的走线横截面的效果图(如果不能理解请别做设计了), 当你选用的计算模型计算好后, 你画板设计的走线环境一定要同模型匹配. 参考层: 阻抗线同位置处遇到的第一个铺了地铜(有的是网格)的层称之为参考层, 这些地铜相对于阻抗线也有称它为信号屏蔽层. 案例二: 嘉立创7628结构, 4层板, 1.6板厚, 外层100ohm的差分阻抗, 线宽线距该如何设计? 看下图多了两个数据项 S1: 走线间距 C3: 走线间的基材上的阻焊厚度, 注意走线间隙一般比较小, 容易产生沟壑效果, 这里的阻焊厚度稍微厚一点. 其它数据项同上面单端一样. 下图中的计算结果表示线宽/线距设计成8mil/8mil即可达到100ohm的阻抗值要求, 当然你可以通过调整不同的线宽/线距值组合, 也能得到相同的100ohm值, 自已凋整算吧.

案例三: 嘉立创7628结构, 4层板, 1.6板厚, 内层50ohm的单端阻抗, 线宽该设计多宽? 见下图 H1: 芯板的Core厚度 Er1: 芯板的介电常数 H2: 7628PP的厚度, 8.5是指 PP厚度+内层线路铜厚 7.6 + 0.5 = 8.1mil, 为什么铜厚是0.5mil, 是因为取的残铜率后取的平均值, 是个估值, 按我的经验这样计算没毛病. Er2: PP的介电常数 T1: 内层铜厚 下图的效果表示 9.5mil的线宽设计可达到50ohm的阻抗需求. 结合此模型及上面的参数数据, 此阻抗线设计在内层时, 两面的参考层一个是外层, 一个是相邻的内层. 如果两的参考层都是外层线路, 那么H1就表示的是第二层线路到第四层线路间的介质厚度总和了, 不能像下图这样填写. 说这么啰嗦就是想不断的提醒你, 不管用什么模型, 你脑子里面都要有一个空间想像图, 模型同叠层结构做匹配, 参数怎么填写, 是看走线的实际环境和叠层结构的. 内层的差分计算就不再做介绍了, 请大家自已举一反三.

共面阻抗介绍 单端的还有一种计算模型是共面阻抗(差分的共面情况同单端的道理一样), 如下图 多了一个参数D1, 表示走线距旁边地铜的间距, 走线旁边两边表示的是地铜大铜皮 还有一种共面模型是, 走线两边是走线, 如下图 多了一个参数G2, 这表示走线周围是被等距的走线包围的, G2就是包围走线的宽度 下图这种也是共面, 但是它没有参考层, 记住共面阻抗是可以没有参考层的

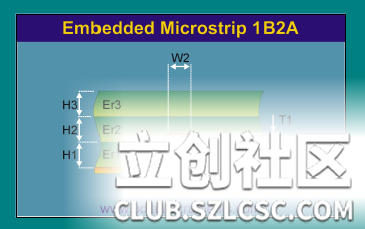

连续的多介质的计算模型介绍 像下图, H2一般是表示紧挨外层的PP厚, H2与H1之间是肯定有一层线路的, 只是阻抗线这里的铺铜避开了, 所以H1是表示这层线路到下一参考层线距间的介质厚度总和, 参考层可以是第三层线路, 也可以是第四层线路等等, 参考层在哪一层是由你来设计的. 像下图, 很多新手分不清哪一层介质表示PP, 其实有一个很简单的规则, 被走线嵌入的介质肯定是PP, 下图H2就表示是PP, 那么以此推导H1,H3就肯定表示芯板的基材了. 再来一个模型, 猜猜哪个介质是PP? 没有阻焊的外层计算模型 见下图的计算模型 外层阻抗有阻焊没阻焊计算的阻抗值是不一样的, 一般是PCB工厂使用的, 刚蚀刻完线路还没有印刷阻焊, 这个时候也可以测试阻抗, 用来监控制造过程. 但是如果你的板子也要求不印阻焊, 那么就得选用这种模型来计算阻抗了.

先分享到这儿吧! |

|||

dabaosod18

0

主题

3

回复 |

2#

mark

|

|||

沐阳展颜

6

主题

821

回复 |

3#

企业微信:18681568525 冯工 注册下单www.sz-jlc.com/r [业务代号R]

一扇打开新世界的大门,电子产品从这里开始...

|

|||

nicole088

0

主题

2

回复 |

4#

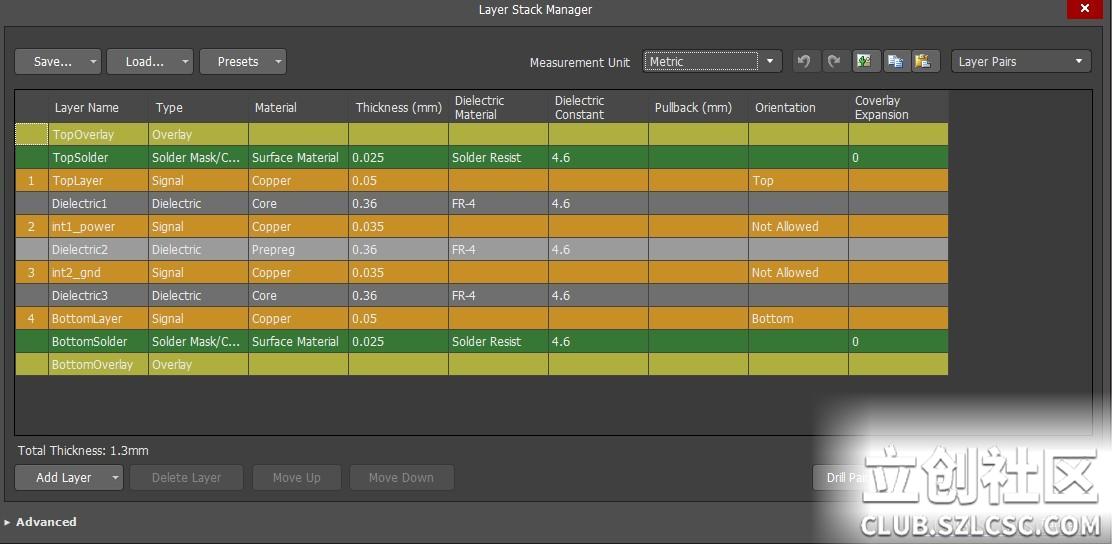

AD18默认的层压结构如下,怎么修改成2312层压结构?压合PP是不是下面的Dielectric.

|

|||

Wattle0Hua

6

主题

110

回复 |

5#

终于有详细的层叠指导了,这贴子好!Mark!

|

|||

GUO

GUO

【官方工作人员】

24

主题

193

回复 |

6#

忽略AD里面的叠层管理,只要你的线路层顺序没有搞错就行了. 除了层排序,PCB厂商提供了压合结构(比如嘉立创提供的),你按这个结构下单做板就行了,软件默认的结构不管它. |

|||

chenguoan

0

主题

1

回复 |

7#

这个残铜率是该减还是加啊,之前看到一个教学是减去残铜率

|

|||

GUO

GUO

【官方工作人员】

24

主题

193

回复 |

8#

有一个技巧,看你要计算的PP厚度测量范围 一:如果这个测量范围包含了走线层,那就是要加 如下图H2的厚度测量范围是包含了走线厚度的 二:如果这个测量范围不包含走线层,那就是要减, 如下图 |

|||

njyq2008

2

主题

68

回复 |

9#

” 连续的多介质的计算模型介绍 像下图, H2一般是表示紧挨外层的PP厚, H2与H1之间是肯定有一层线路的, 只是阻抗线这里的铺铜避开了, 所以H1是表示这层线路到下一参考层线距间的介质厚度总和, 参考层可以是第三层线路, 也可以是第四层线路等等, 参考层在哪一层是由你来设计的. ” 楼主你好,关于这一段论述,本小白想请教一下,如果顶层走线按共面波导画,下面的几层都没有铺地,也就是说走线下是PP、Core、PP,然后底层是参考地,这种情况下,如何计算阻抗呢? P.S. 我个人从做传统电源被迫转行做射频相关,刚接触相关的东西,有个射频的功放需要和控制电路想画一块板上,功放部分功率较大、线需要走宽一些,这样介质就需要厚一点以满足阻抗的要求,而剩下的部分都是控制电路,内层铺地,因此就有上述问题。

低成本高性能电流检测方案 INA180 http://club.szlcsc.com/article/details_10515_1.html

|

|||

GUO

GUO

【官方工作人员】

24

主题

193

回复 |

10#

只有介质厚度有变化,其它同上面计算方式一样

|

|||

njyq2008

2

主题

68

回复 |

11#

就是说还是按两种介质的模型来算就成,只要把同种材料的厚度合并起来算就可以哈?

低成本高性能电流检测方案 INA180 http://club.szlcsc.com/article/details_10515_1.html

|

|||

永远是菜鸟

0

主题

3

回复 |

12#

隔层阻抗设计时,芯板的介电常数按多少来算呢

|

|||

GUO

GUO

【官方工作人员】

24

主题

193

回复 |

13#

有个复杂的计算算法,总的来说是,根据各介质厚度及介电常数综合计算出一个折中的平均值. 但是据我的观察经验,一般情况下是取最大的那个介电值,也没什么太大的毛病. |

|||

jimwon

1

主题

3

回复 |

14#

案例一: 嘉立创7628结构, 4层板, 1.6板厚, 外层50ohm的单端阻抗, 线宽该设计多宽?

结论是线宽11.5mil,请问覆铜间距如何设置?

|

|||

快雪时晴A

0

主题

8

回复 |

15#

家里创的文档里面压合PP的厚度是0.2mm. 而例子中使用的厚度是7.1mil 两者是有差别的呀?到底取哪个?

|

|||

快雪时晴A

0

主题

8

回复 |

16#

那个,请问走线的铜厚是怎样得到的?是1盎司 = 1.4 0.5盎司 = 0.7这样吗?

|

|||

快雪时晴A

0

主题

8

回复 |

17#

我又看了下,表格下方有说明是取7.1mil

|

|||

快雪时晴A

0

主题

8

回复 |

18#

我查了下,1盎司 = 35um =0.035mm = 1.3779mil 近似到14的吗?

|

|||

快雪时晴A

0

主题

8

回复 |

19#

这篇文章实在是太解渴了!!!!!

|

|||

星火燎原

0

主题

16

回复 |

20#

可否把你们做阻抗测试的PCB的源文件共享出来看看,或者画几个常用示例

|

|||

jimwon

1

主题

3

回复 |

21#

我这个问题请高手帮忙解答下哦

|

|||

GUO

GUO

【官方工作人员】

24

主题

193

回复 |

22#

如果不想覆铜对单端阻抗造成影响,据我的观察,覆铜至少要保证距走线20mil的间距。 其实看了我的文章,你自已也可以解决这个问题,所谓覆铜距走线其实就是共面的模块场景,你找到最接近的场影计算模块,你不断的调大覆铜与走线的间距就会发现,当这个间距值大到一定的程序,计算得到的阻抗结果变化基本上就不大了,那么这个间距可以理解为安全间距 |

|||

青风123

1

主题

1

回复 |

23#

设计外层阻抗时,铜皮到线的距离怎么确定?和线间隙一样还是没有要求?

|

|||

徜徉100

0

主题

1

回复 |

24#

带过孔得怎么搞!

|

|||

GUO

GUO

【官方工作人员】

24

主题

193

回复 |

25#

请参考你楼上的回复别人的答案,这个答案也适用于你的问题

|

|||

花好月圆

2

主题

81

回复 |

26#

2层板的如何计算?

|

|||

喝最柔的酒

1

主题

91

回复 |

27#

4层板选择了7628阻抗匹配,板厚1.6mm,计算结果11.55mil。使用此值进行阻抗匹配时,是否还需要保留PI电路?

|

|||

GUO

GUO

【官方工作人员】

24

主题

193

回复 |

28#

我只关注走线的实际场景,是否同计算模型匹配。 你说的这个什么PI电路我就不懂了,留给高手来解答 |

|||

你的付哥哥

2

主题

9

回复 |

29#

辛苦了!这篇文章值得我请作者喝顿酒!好人啊!写的这么细!

|

|||

GUO

GUO

【官方工作人员】

24

主题

193

回复 |

30#

我这个人很实心眼儿,别人说的话都会当真的,别忘记了兑现你的承诺

|

|||

你的付哥哥

2

主题

9

回复 |

31#

肯定!

|

|||

430lpy

0

主题

2

回复 |

32#

请问我计算共面阻抗,算出来的线宽比元器件的引脚宽可以吗?截图是我的参数(单位:mil)。。 我最小的引脚是sot23的二极管的,宽度是0.3mm.

|

|||

430lpy

0

主题

2

回复 |

33#

|

|||

雨过等天晴

0

主题

4

回复 |

34#

第二层不铺铜?参数模型确定是这个?没有参考层? |

|||

阿皮哥2007

3

主题

3

回复 |

35#

mark 一下下,楼主好人

|

|||

Bigpig

0

主题

1

回复 |

36#

mark 一下下,学习了

|

|||

cd837

0

主题

1

回复 |

37#

您好! 我有一块板要做阻搞匹配?有偿帮忙.急. 谢 联系电话:1354332923久(同微信) |

|||

LQ202

0

主题

1

回复 |

38#

mark

|

|||

拉线工程师

0

主题

1

回复 |

39#

阻抗计算神器的6层板,内层计算数据是不是有问题???50欧阻抗要20mil?

|

|||

hdcqm

0

主题

1

回复 |

40#

只想点个赞

|

|||

qqzhu

0

主题

1

回复 |

41#

楼主:我是小白,对于参考层有些疑惑,我是四层板,中间两成是电源层和地层,其中电源层可以作为参考层吗?

|

|||

GUO

GUO

【官方工作人员】

24

主题

193

回复 |

42#

Si9000给的是一个客观理论,它只提供在一种理想状态下的阻抗结果,根据精心设计的阻抗条来验证结果是很准的。 对PCB制造来说,只要符合Si9000的模块规范,理论上任何层都可以做为参考层,但实际上Si9000给的规则只能保证你不符合它阻抗是肯定得不到你想要的结果,你符合它的规则不一定能保证你的结果。 因为影响阻抗的因素还有很多:除了材料/生产公差是厂家在管控,你的设计也有很大因素,阻抗线是否足够长,周围是否有其它干扰因素(比如过孔,元件布局)。 我以前接触过很多工程师都是在不断的改进设计来达到自已想想要的阻抗结果,现在打样也便宜,你可以多几次样测试验证你的设计。 |

|||

电路工程

0

主题

1

回复 |

43#

请问一下在嘉立创打样的FR-4双面板,板厚1.6MM,无铅喷锡,能做50欧姆阻抗匹配吗?因为好多WIFI,蓝牙的PCB板载天线,都是50欧姆,我看了别家做出来是这样的线宽0.8MM,跟敷铜的间距是0.2032MM,这样配配出来是50欧姆吗?谢谢

|

|||

KCC123

1

主题

130

回复 |

44#

您好,影响阻抗的因素较多,其中板厚是一个,双面板的板厚公差相对多层板间的PP片厚度来说比较大,具体可以用SI9000结合我司参数来计算,谢谢!

|

|||

Allenx5

6

主题

14

回复 |

45#

mark

|

|

发表于2018-03-10 08:53:30

发表于2018-03-10 08:53:30

收藏

收藏