|

查看:

3403

|

回复:

2

|

关于LCEDA的一些BUG描述和一些改善建议

|

SuLeiHE

2

主题

1

回复 |

1#

电梯直达

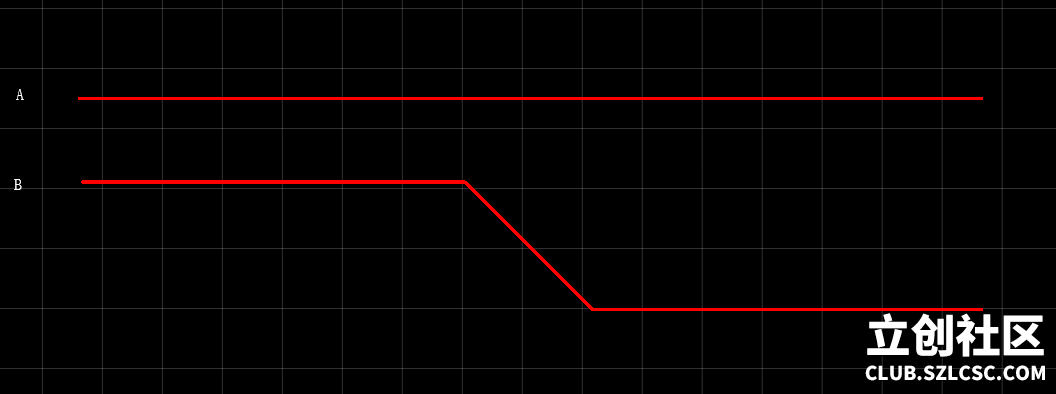

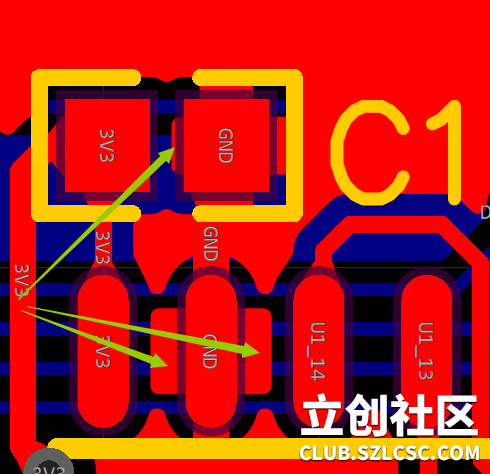

各位LCEDA的工程师大佬们辛苦啦! 作为一个使用两年多的用户来反馈一些问题,这些问题在我开发的时候确实困扰到我了,有些问题甚至令人心情崩溃。下面我详细列举并描述: 一、原理图设计(愉快的使用感受) 1.A2、A1、A0纸张时,纸张拖动和缩放非常卡 2.同上,在画导线后结束绘画(即点击鼠标右键)会有明显卡顿 二、PCB设计(接近崩溃) 1.大工程卡,真的是卡(什么是大工程我这边也不好下定义,比如画一个arduino uno r3的板子算是小工程,一点都不卡;比如画一个nuc972的板子(亦或是stm32f429+sdram+lcd rgb888+nand flash+ethernet)算是大工程(非常卡)。 2.具体卡的方面体现在:拖动和缩放画布卡、拖动元器件位置卡、打开工程慢、敷铜慢、3D预览慢 3.重点在于拖动画布卡,这个问题分又分两种情况,一是不在布线的时候拖动画布也是很卡,有时能够卡到假死2-3秒;二是在布线的时候,由于导线比较长,需要拖动画布继续延申,这时候有很高的概率在拖动画布后在绘制状态的导线消失了,得从头再画。 4.接着上述第3点后半个问题,那我在绘制导线后让他结束绘制(即点击鼠标右键,让在绘制状态的导线变为实际PCB上的导线),拖动画布后再接着画,这个操作本身没有问题,但是如果后续调整走线(比如把几根平行的导线捋捋顺,把间隔调整到一致),这时候在之前几次绘制的同一根导线会出现不属于同一段的问题,拖动这跟导线,导线会在中间弯折。如下图所示,导线A,一根笔直的导线,但是由两次绘制而成,此时拖动导线A位置,有很高的概率会出现B所示的情况,在中间弯折了。 5.过孔吸附和网络归属问题,过孔自动吸附到导线端点功能还需要加强一些,经常出现不自动吸附(当然同时也就出现了无网络归属的过孔了)。另外,比如顶层和底层都是铜箔地,在这儿打上过孔,过孔网络应该自动识别为地,现在还不能这样自动识别,需要手动设置过孔归属网络。 6.过孔尺寸最好能记忆,每次打开工程会导致过孔尺寸恢复到默认的尺寸 7.敷铜规则最好能再优化一下,主要解决下图所示问题 8.在画完导线再进行微调时有很高的概率出现笔直的导线分段问题和转弯的导线出现任意角度的问题(即非135度走线)。 9.在使用时间长一点时(比如连续使用3个小时?5个小时?)会有很多玄学问题,多数是显示bug,不太好描述,后续及时截图后再反馈吧。出现这种问题也好解决,保存一下当前的工程,把网页关掉,再重新打开,就可以了。 总结一下,主要需要解决和改善所谓”大工程“很卡的问题和”导线“问题。这两个问题让人在画稍复杂一点的板子时非常崩溃。总体来说,现在这个版本下,LCEDA画原理图是个愉快的体验,画中等规模或是小规模的PCB也是愉快的体验,但是要想画”稍有规模“的PCB真的要做好思想准备。 上述对PCB规模的定义是我自己的理解,PCB大佬们勿喷,比不了你们的8层及以上板子的复杂度。我这也是在最近画完一块100mm*190mm的”稍微复杂一点”的PCB后觉得一定要给LCEDA工程师们一个反馈了。因为LCEDA好用,所以希望LCEDA能发展的越来越好。 我使用的电脑系统win7 win10都有,我使用的电脑CPU i5-4210U i7-9750H等(还有一些台式机的,总体来说都不算太差),内存都在8G及以上,网络是移动100M光纤,电信100M光纤等,浏览器统一是Chrome。上述问题在这几种电脑环境中都存在,不是个例,和电脑性能应该没有多大关系。 各位LCEDA的工程师,辛苦了。谢谢你们!

|

EDA老贺

EDA老贺

7

主题

1500

回复 |

2#

感谢 ,原理图建议不要用A1 A2 图纸,把一个工程拆分为多个原理图。 PCB 或则其他的卡顿,我们已经在研发一套新的设计引擎,性能会提高10倍以上,这个是目前EDA最大的问题,上线时间待定。 这个月会上线一个6.3的小版本,性能会有一定的改善。 其他体验上的问题,我们产品负责人会回复。

|

立创EDA罗工

立创EDA罗工

78

主题

4623

回复 |

3#

你好,感谢写这么长的反馈。 一、原理图设计(愉快的使用感受) 1.A2、A1、A0纸张时,纸张拖动和缩放非常卡 请不要把多个图纸放在一个页面里面,元素多了会非常卡的,用多页的方式,左下角有增加页的按钮。 2.同上,在画导线后结束绘画(即点击鼠标右键)会有明显卡顿 同上 二、PCB设计(接近崩溃) 1.大工程卡,真的是卡(什么是大工程我这边也不好下定义,比如画一个arduino uno r3的板子算是小工程,一点都不卡;比如画一个nuc972的板子(亦或是stm32f429+sdram+lcd rgb888+nand flash+ethernet)算是大工程(非常卡)。 目前PCB比较吃CPU,如果配置好一点的,2000个焊盘基本不卡顿的,明年会出新引擎,10w焊盘也不卡顿 2.具体卡的方面体现在:拖动和缩放画布卡、拖动元器件位置卡、打开工程慢、敷铜慢、3D预览慢 画布元素太多了,产生大量计算和渲染,吃CPU配置 3.重点在于拖动画布卡,这个问题分又分两种情况,一是不在布线的时候拖动画布也是很卡,有时能够卡到假死2-3秒;二是在布线的时候,由于导线比较长,需要拖动画布继续延申,这时候有很高的概率在拖动画布后在绘制状态的导线消失了,得从头再画。 同上 4.接着上述第3点后半个问题,那我在绘制导线后让他结束绘制(即点击鼠标右键,让在绘制状态的导线变为实际PCB上的导线),拖动画布后再接着画,这个操作本身没有问题,但是如果后续调整走线(比如把几根平行的导线捋捋顺,把间隔调整到一致),这时候在之前几次绘制的同一根导线会出现不属于同一段的问题,拖动这跟导线,导线会在中间弯折。如下图所示,导线A,一根笔直的导线,但是由两次绘制而成,此时拖动导线A位置,有很高的概率会出现B所示的情况,在中间弯折了。 你分开两次画导线了,一次性画完的导线是不会有的,或者分两次画的产生自动合并导线后也不会有,应该是有场景不支持自动合并导线,比如,一段导线大一段小;端点没有重合在一起的 5.过孔吸附和网络归属问题,过孔自动吸附到导线端点功能还需要加强一些,经常出现不自动吸附(当然同时也就出现了无网络归属的过孔了)。另外,比如顶层和底层都是铜箔地,在这儿打上过孔,过孔网络应该自动识别为地,现在还不能这样自动识别,需要手动设置过孔归属网络。 在铺铜上放过孔是特意没有支持的自动计算网络,这个会非常卡和耗时,计算过孔下方的元素的网络不是很好计算的,要考虑其他层,其他导线,其他元素的各种交叉问题。你如果需要缝合孔可以点击铺铜线在属性那里有“放置过孔”按钮,你会看到放置时非常慢。 6.过孔尺寸最好能记忆,每次打开工程会导致过孔尺寸恢复到默认的尺寸 以后会支持模板 7.敷铜规则最好能再优化一下,主要解决下图所示问题 这个突出的热焊是铺铜算法的目前不支持,热焊宽度设置在6.3会支持 8.在画完导线再进行微调时有很高的概率出现笔直的导线分段问题和转弯的导线出现任意角度的问题(即非135度走线)。 基本同第4 9.在使用时间长一点时(比如连续使用3个小时?5个小时?)会有很多玄学问题,多数是显示bug,不太好描述,后续及时截图后再反馈吧。出现这种问题也好解决,保存一下当前的工程,把网页关掉,再重新打开,就可以了。 好的 总结一下,主要需要解决和改善所谓”大工程“很卡的问题和”导线“问题。这两个问题让人在画稍复杂一点的板子时非常崩溃。总体来说,现在这个版本下,LCEDA画原理图是个愉快的体验,画中等规模或是小规模的PCB也是愉快的体验,但是要想画”稍有规模“的PCB真的要做好思想准备。 我们之前的目标就是小板子设计的。。然后大家越画越大 上述对PCB规模的定义是我自己的理解,PCB大佬们勿喷,比不了你们的8层及以上板子的复杂度。我这也是在最近画完一块100mm*190mm的”稍微复杂一点”的PCB后觉得一定要给LCEDA工程师们一个反馈了。因为LCEDA好用,所以希望LCEDA能发展的越来越好。 我使用的电脑系统win7 win10都有,我使用的电脑CPU i5-4210U i7-9750H等(还有一些台式机的,总体来说都不算太差),内存都在8G及以上,网络是移动100M光纤,电信100M光纤等,浏览器统一是Chrome。上述问题在这几种电脑环境中都存在,不是个例,和电脑性能应该没有多大关系。 新引擎预计明年这个时候会公测,10w焊盘规模不会卡

技术支持微信:请前往lceda.cn获取二维码,官方群:不再提供QQ群,公众号:立创EDA 或 开源硬件平台

|

|

发表于2019-10-13 23:56:36

发表于2019-10-13 23:56:36

收藏

收藏