|

查看:

1272

|

回复:

1

|

静态随机存储器SRAM存储数据原理

|

|

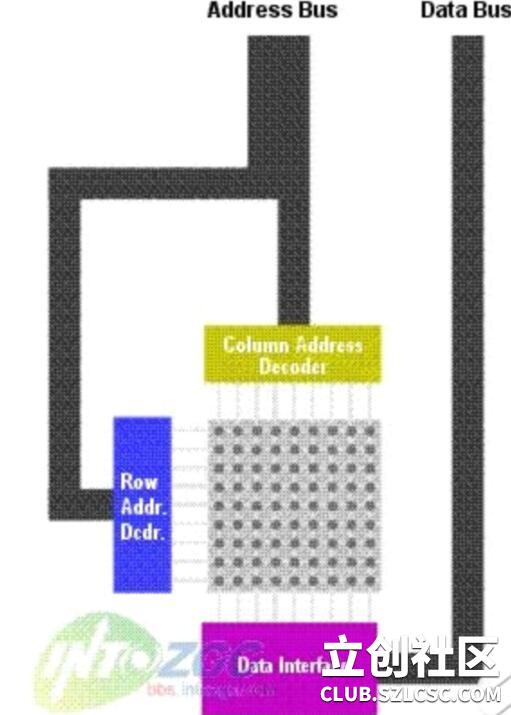

1#

电梯直达

RAM主要的作用就是存储代码和数据供中央处理器在需要的时候进行调用。对于RAM等存储器来说仍是一样的,虽然存储的都是代表0和1的代码,但是不同的组合就是不同的数据。对于RAM存储器而言数据总线是用来传入数据或者传出数据的。因为存储器中的存储空间是如果前面提到的存放图书的书架一样通过一定的规则定义的,我们可以通过这个规则来把数据存放到存储器上相应的位置,而进行这种定位的工作就要依靠地址总线来实现了。 对于中央处理器来说,RAM就象是一条长长的有很多空格的细线,每个空格都有一个唯一的地址与之相对应。如果中央处理器想要从RAM中调用数据,它首先是需要给地址总线发送地址数据定位要存取的数据,然后等待若干个时钟周期之后,数据总线就会把数据传输给CPU。下面关于SRAM存储原理示意图可以帮助我们很好的理解这个过程。 图1 上面图1所列举的例子中CPU在一行数据中每次只是存取一个字节的数据,但是在现实世界中是不同的,通常CPU每次需要调用32bit或者是64bit的数据(这是根据不同计算机系统的数据总线的位宽所决定的)。如果数据总线是64字节的话,CPU就会在一个时间中存取8个字节的数据(想一想,如果每次还是存取1个字节的数据,64bit总线将不会显示出来任何的优势。) 上图中的小圆点代表RAM中的存储空间,每一个都有一个唯一的地址线同它相连。当地址解码器接收到地址总线传送来的地址数据之后,它会根据这个数据定位中央处理器想要调用的数据所在的位置,然后数据总线就会把其中的数据传送到中央处理器。 图2 如果RAM对于CPU来说仅仅是一条“线”的话,还不能体现实际的运行情况。因为如果实际情况真的是如此的话,在实际制造芯片的时候,会有很多实际的困难,特别是在需要设计大容量的RAM的时候。所以一种更好的能够降低成本的方法是让存储信息的“空格”排列为很多行--每个“空格”对应一个bit存储的位置。如果要存储1024bits(2^10)数据,那么你只要使用32x32(2^5*2^5=2^10)的矩阵就能够达到这个目的了。很明显一个32x32的矩阵比一个1024bit的行设备更紧凑,实现起来也更加容易。请看图2. |

|

2#

果RAM对于CPU来说仅仅是一条“线”的话,还不能体现实际的运行情况。因为如果实际情况真的是如此的话,在实际制造芯片的时候,会有很多实际的困难,特别是在需要设计大容量的RAM的时候。所以一种更好的能够降低成本的方法是让存储信息的“空格”排列为很多行--每个“空格”对应一个bit存储的位置。如果要存储1024bits(2^10)数据,那么你只要使用32x32(2^5*2^5=2^10)的矩阵就能够达到这个目的了。很明显一个32x32的矩阵比一个1024bit的行设备更紧凑,实现起来也更加容易。

|

|

发表于2020-02-21 16:19:00

发表于2020-02-21 16:19:00

收藏

收藏