|

查看:

1466

|

回复:

1

|

SRAM整体结构图

|

是酒窝啊

196

主题

231

回复 |

1#

电梯直达

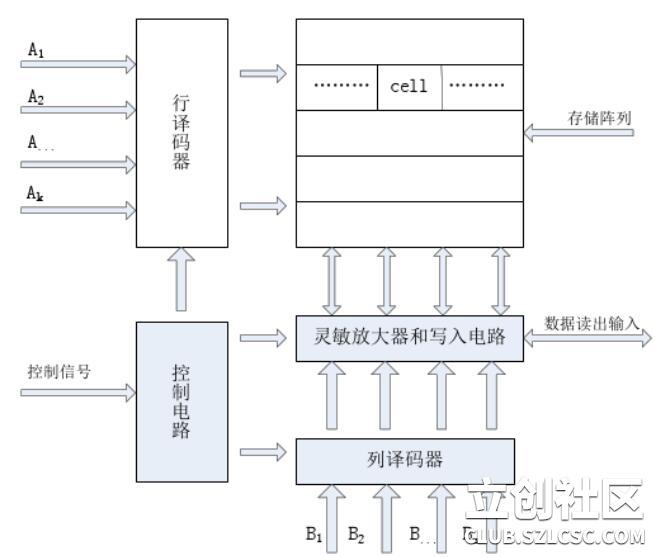

SRAM大多是由CMOS管组成的挥发性静态存储器。在掉电后存储器中所存数据就会丢失。随机静态存储器可以对任何地址进行读写操作,通过锁存器的原理对数据进行保存,在无操作状况下,锁存器处于稳态,保持数据稳定,不用进行周期性的电荷刷新。SRAM由基本单元构成的阵列以及外围电路构成,其中阵列的划分和外围电路的优劣对整个SRAM的性能有很大的影响。 SRAM是随机存储器的一种,它由静态挥发性存储单元组成的存储阵列(或者叫内核,core) 组成,其地址译码集成在片内。SRAM 速度很快而且不用刷新就能保存数据不丢失。它以双稳态电路形式存储数据,结构复杂,内部需要使用更多的晶体管构成寄存器.以保存数据。SRAM由于靠连续的供电来维持所存数据的完整性,故属于易挥发性存储器。 SRAM电路结构与操作和一般的RAM类似,由存储阵列、灵敏放大器、译码器、输入输出电路和时序控制电路五大部分组成。存储单元按行和列排列起来就组成了sram芯片的阵列结构,行和列分别称为“字线”和“位线”。每个存储单元对应于一个唯一的地址,或者说行和列的交叉就定义出了地址,而且每一个地址和某一特定的数据输入输出端口是相连的。一个存储芯片上的阵列(或者自阵列)数目是由整个存储器的大小、数据输入输出端口数目、存储速度要求、整个芯片的版图布局和测试要求所决定的。 图1 SRAM 的整体结构图 如图1所示存储阵列是由存储单元(cell)构成的矩形阵列。每一个单元都有自己独特的地址,通过外围的译码电路选中相应的单元进行读写操作。译码电路包括行译码电路和列译码电路,其中行译码电路用来从2* 行中选中一行,列译码是从2* 中列中选出一-列。这样通过行译码列译码的共同作用来从阵列中选出相应的单元进行读写操作。灵敏放大器和写入电路用来对数据进行读写操作。 在数据读出过程中,由于位线过长使得从单元中读出的信号很弱,需要用灵敏放大器来放大信号,加快数据的读出过程。写入电路用来进行数据的输入。控制电路主要用来控制数据的读写以及译码过程。通过相应的控制信号如读使能信号写使能信号等来控制数据的读写操作。

宇芯电子主要产品线有静态随机存储器SRAM,非易发性存储器MRAM,伪静态存储器PSRAM等多种类型随机记忆体及微控制器MCU等半导体产品,189-2655-4009

|

是酒窝啊

196

主题

231

回复 |

2#

SRAM大多是由CMOS管组成的挥发性静态存储器。在掉电后存储器中所存数据就会丢失。随机静态存储器可以对任何地址进行读写操作,通过锁存器的原理对数据进行保存,在无操作状况下,锁存器处于稳态,保持数据稳定,不用进行周期性的电荷刷新。SRAM由基本单元构成的阵列以及外围电路构成,其中阵列的划分和外围电路的优劣对整个SRAM的性能有很大的影响。

宇芯电子主要产品线有静态随机存储器SRAM,非易发性存储器MRAM,伪静态存储器PSRAM等多种类型随机记忆体及微控制器MCU等半导体产品,189-2655-4009

|

|

发表于2020-06-08 16:29:33

发表于2020-06-08 16:29:33

收藏

收藏