|

查看:

4728

|

回复:

2

|

6层阻抗板设计(微带单端75欧姆,微带差分100欧姆阻抗板)

|

|||

阿皮哥2007

3

主题

3

回复 |

1#

电梯直达

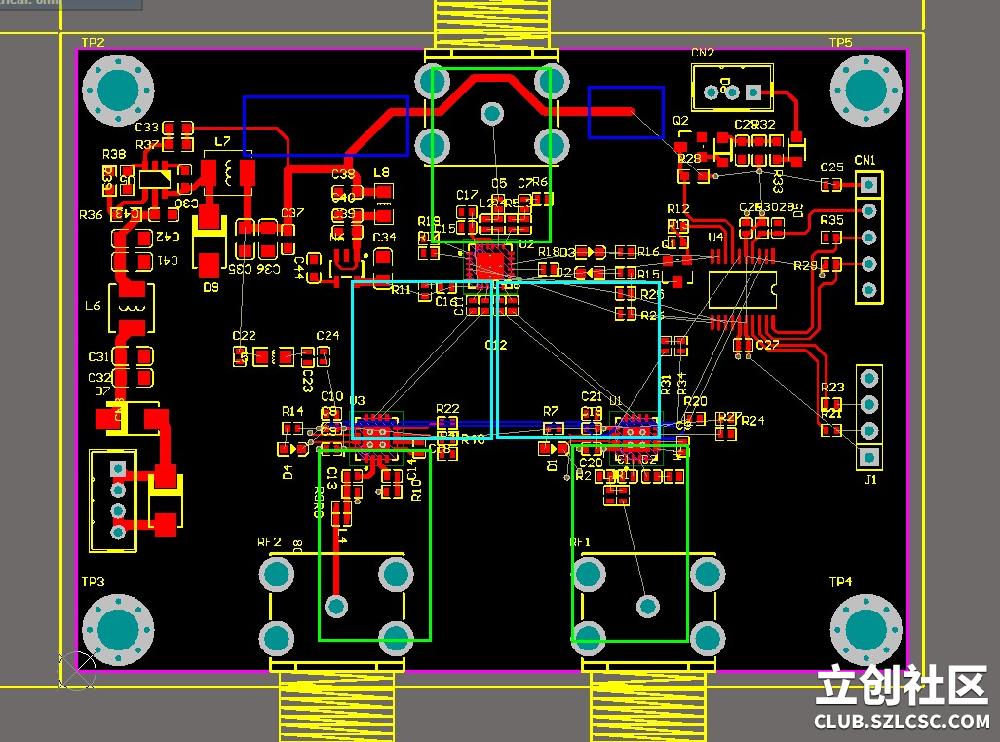

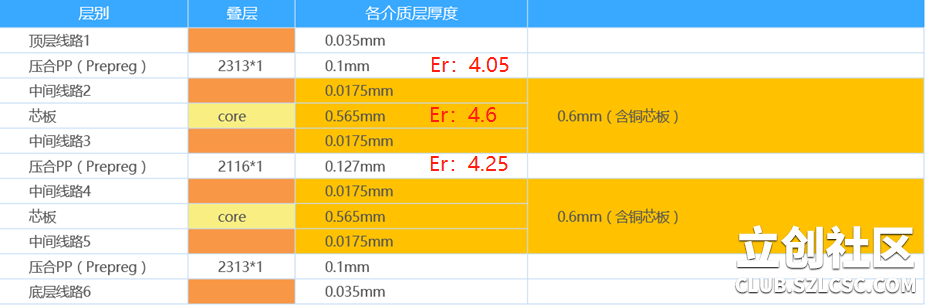

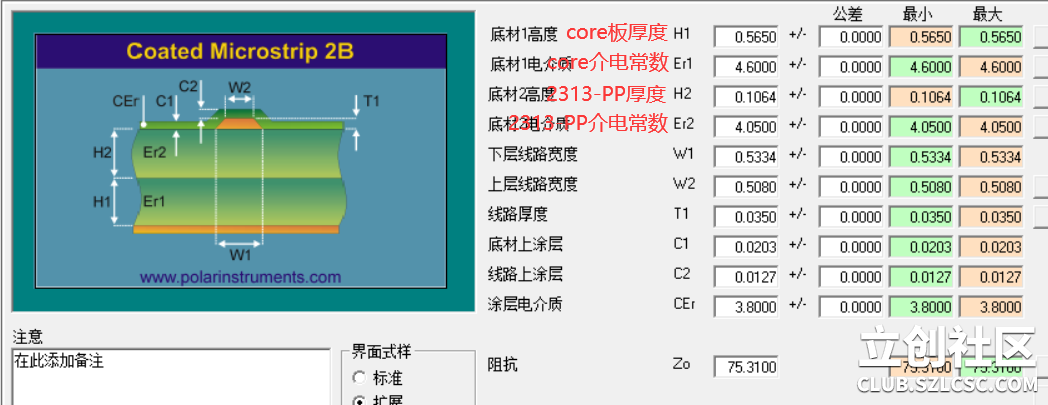

现需要设计一款SDI高清视频的2选1的收发板,信号频率最高到3G,板子上采用75欧姆的BNC接口输入,线路75欧姆,中间一级有差分100R的阻抗线路,再BNC,75欧姆阻抗输出。一共有3个地方需要做阻抗线。做硬件也很多年,但是阻抗板是第一次做,所以经验几乎为0,算是小白了吧。加上这个板子要做的阻抗有3个地方,信号带宽到了3G,在看来有点复杂了。所以,非常希望有经验的高手能指点指点,非常感谢! 现在规划情况: 1. 板层:6层,板厚:1.6mm 2. 叠层的规划: Z1-G2-G3-P4-G5-S6,其中Z代表阻抗信号层,G是地平面,P电源层,S是一般信号层。 都用微带方式来做, 因为嘉立创板层结构固定死了,使用Z1-G2(G2参考地层)组合,板层太薄了,无法实现75R的阻抗,输入和输出的75R打算用Z1-G3(G3参考地层)来做, 100欧姆的差分使用Z1-G2(G2参考地层)来做. 3. 板子布局如下: 3个绿色框部分是75欧姆阻抗线路, 青色是100欧姆的阻抗线路 现在几个问题: 1. 关于器件封装对阻抗的影响, 其1, BNC接口的信号线焊接到版上的焊盘直径肯定会比计算出来的线宽要宽,这个点的阻抗也肯定会比75欧姆小.其2, 阻抗线路上的贴片电阻焊盘大小也可能会比线宽要宽. 也会呈现出低阻抗的情况, 这样一来,阻抗的连续性就会被打破, 因为SDI是视频信号,信号有问题,是可以直接从显示结果看出来. 我想了解的是对于3G的信号来说, 这些因为器件封装导致的阻抗变化,影响会有多大? 2. 关于布局, 阻抗线路从布局角度来说,线越短越好,但是因为结构限制,板子就这个大小,无法更改. 从权衡性能的角度来说, 上图中的75欧姆和100欧姆的阻抗线路,是否是缩短单端的线路会更好呢? 毕竟差分线路的抗扰能力比单端的要好. 3. 关于75欧姆跨层阻抗的PP层的厚度问题,嘉立创的6层板叠层如下: 用SI9000来计算 75欧姆计算模型如下图: 图中H2对应的是2313-PP层, 因为该层下面的”中间选路2”的敷铜被挖去,那么H2的高度,是否需要加上这个0.0175mm的铜厚呢? 图中的计算结果我是加上这个铜厚的, 2313-PP层在压合后,使用3.5mil的厚度计算的话,就是3.5mil + 0.0175mm = 3.5+0.689mil = 4.189mil=0.1064mm. 这里不确定是不是应该加上这个铜的厚度? 希望有经验的人可以指点指点.非常感谢. 最后: 因为第一次设计阻抗板,希望大家就这个板子,能多指教指教,再此,先感谢大家啦 |

|||

萧规曹随

6

主题

328

回复 |

2#

楼主可仔细看下所用的芯片和BNC座子的datasheet,估计里面有相关阻抗线的要求及设计方法。 1,封装,焊盘,过孔,部分如扇出走线不满足阻抗要求是一贯性,阻抗不连续未必会直接导致信号损耗或时序不满足要求,信号传输完整性受多方影响。 2,如果阻抗走线在天线或取样等小信号路径,估计要射频工程师依仿真给出最优方案;视频输出的话,要求会低些。 3,阻抗计算,找几个芯片大厂的有高速部分的参考设计,就能参照处理了。

提供LCEDA,99SE,DXP,Pads,Allegro平台PCB设计;光绘文件还原可编辑的PCB

|

|||

阿皮哥2007

3

主题

3

回复 |

3#

非常感谢你给的宝贵意见,我这边在Ti的官网找到2个demo PCB说明,我先参考他的来画,后面实际看看测试效果如何吧。

|

|

发表于2020-07-05 08:50:18

发表于2020-07-05 08:50:18

收藏

收藏