|

查看:

4761

|

回复:

8

|

反映EDA应用过程的几个BUG

|

三贝计算

1

主题

3

回复 |

1#

电梯直达

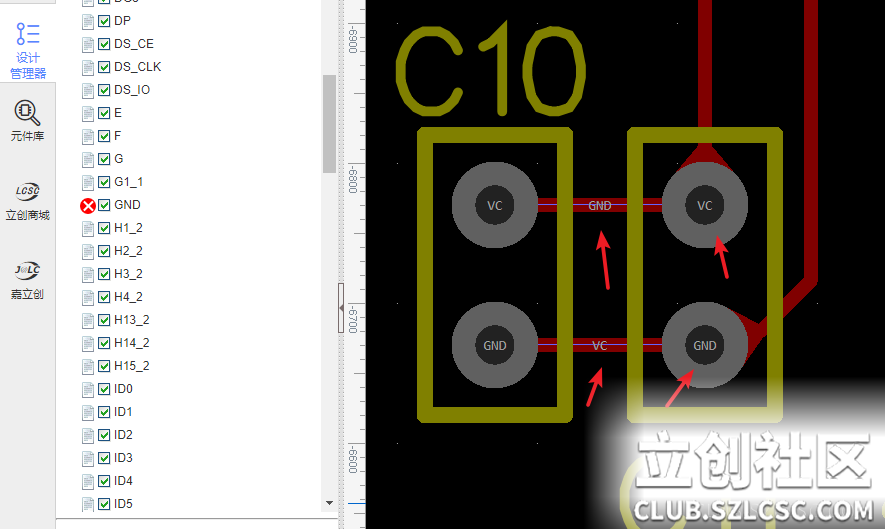

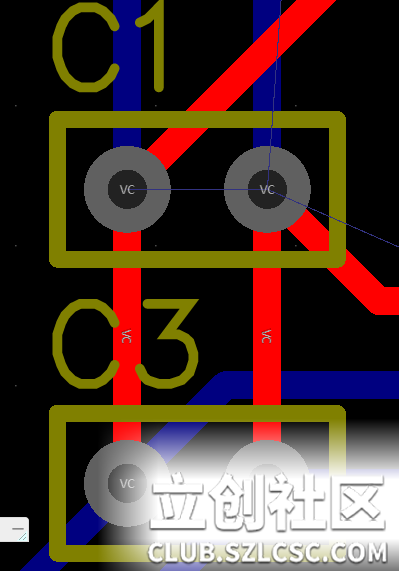

1)为什么重新导入PCB时NET会发生错乱?同一封装的不同NET会错乱,(发生此情况是PCB手动布线已基本完成,修改原理图后重新更新PCB,就出现这种情况,再次更新也解决不了问题)见图: 图一:此图中两个NET一个是VC,另一个是GND,结果再次更新PCB时变成了两个VC。 图二:明明是并列的两个电容,一个VC和一个GND,结果上面的变成两个VC 图三:一个GND和一个VC变成了两个GND 图4:此图中说明的问题是不仅焊盘的NET乱了,原来布线的NET也错了。 2)同一NET只允许定义一种线宽,这个不太合理,例如:电源的VC在不同元件上消耗电流不一样,需要的线宽也是不一样的:例如:单片机或其他高集成度芯片一般引脚较细,这需要的VC线也必须较细(否则间距不够),而其他功耗较大的芯片则需要较宽的VC。现版本,按不同宽度布线后(当时没事),再次更新PCB时会出现错误,导致不能识别与定义规则不同的线。 3)敷铜能不能不要每次进入PCB就重置,对于个别间距要求较大的封装,必先调大封装,敷铜完毕后将封装改回原尺寸,而现版本每次进入PCB页,自动重新敷铜,导致原来白弄了。 4)敷铜到边框的间距不能设置??对于异形板怎么控制敷铜与边框的问距,像下面这样间距能打样吗? 图一:间距已设置为30mil。 图二:敷铜后是这个样子的

|

立创EDA罗工

立创EDA罗工

78

主题

4623

回复 |

5#

你好。 1、请问你是否在原理图修改了网络名?如果是的话,更新到PCB只会同步更新焊盘的网络,导线的不会变,需要手动修改导线的网络。如果你是说更新到PCB后焊盘的网络也不对的话,麻烦下载一下你的工程发我分析一下。 https://docs.lceda.cn/cn/PCB/Import-Changes/index.html 2、每一个规则设定的是当前的最小线宽,当你相同网络不同导线可以使用不同的线宽,只需比规则的线宽大即可。https://docs.lceda.cn/cn/PCB/Design-Rule-Check/index.html 3、这个为了降低文件体积。你可以画一个小铺铜设置不同的间距给这个封装。 4、暂未支持,以后会支持。目前可以在边框内部铺铜,快捷键L改变铺铜线形状 5、这个会尽快改善掉。

技术支持微信:请前往lceda.cn获取二维码,官方群:不再提供QQ群,公众号:立创EDA 或 开源硬件平台

|

立创EDA罗工

立创EDA罗工

78

主题

4623

回复 |

7#

设计管理器网络报错是因为这段导线和焊盘网络不一致,飞线还在,网络没有连接完毕,所以报错。 设置规则和导入变更是没有关联的,导入变更只更新封装,封装焊盘的。 1.我更改了规则之后,导入更新提示已经匹配,只有原理图有修改才会有导入更新 2.没有复现到。 规则变化,只会影响设计管理器的DRC错误,不会影响设计管理器的网络的。

技术支持微信:请前往lceda.cn获取二维码,官方群:不再提供QQ群,公众号:立创EDA 或 开源硬件平台

|

|

发表于2018-09-11 21:03:16

发表于2018-09-11 21:03:16

收藏

收藏