|

查看:

1215

|

回复:

1

|

赛普拉斯的65nm SRAM与ASIC/FPGA/控制器的接口

|

是酒窝啊

196

主题

231

回复 |

1#

电梯直达

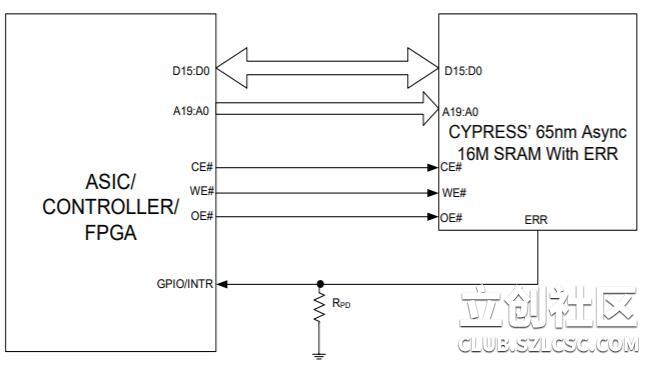

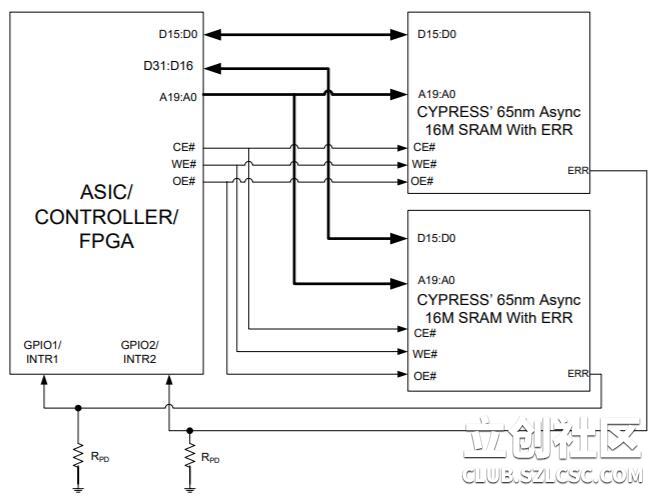

赛普拉斯瞄准的市场增长速度要快于包括汽车,工业和消费电子市场任内的半导体行业。在安全无线技术,连同MCU,存储器,模拟IC和USB控制器,为物联网领域提供了明显的竞争优势,并在新兴市场(包括联网设备和自动驾驶汽车)上实现了飞跃。cypress代理宇芯电子支持提供驱动、例程以及必要的FAE支持等产品服务。 系统设计人员可以使用ERR引脚来监视SRAM中数据的完整性。由于仅当SRAM检测到并纠正了一位错误时才声明ERR信号,因此建议弱下拉该信号以避免在写操作期间或SRAM被禁用时出现中间电压电平。在写周期或芯片禁用周期中,ERR引脚处于HI-Z状态。 1、连接ERR引脚 无需ERR引脚的赛普拉斯SRAM可以像传统SRAM一样在系统中连接。对于具有ERR选项的SRAM,系统设计人员需要在系统中正确连接ERR引脚。如果系统中未使用ERR引脚,则可以将其保持打开状态。本节介绍了在三种基本情况下使用SRAM连接ERR引脚的方法。 •具有单个SRAM的系统 •宽度扩展 •深度扩展 1.1具有单个SRAM的系统 在只有一个SRAM器件连接到板载控制器/ASIC/FPGA4的系统中,可以将ERR引脚连接到ASIC的GPIO/中断引脚。在每个读取周期中,控制器都可以监视ERR引脚的输出。当检测到ERR引脚上的高电平时,ASIC应启动软件子例程以重写从SRAM读取的正确数据。图6显示了此方案的体系结构。 1.2宽度扩展 新一代控制器具有32位数据接口。在这类应用中,系统设计人员可以通过使用两个带有ERR引脚的CYPRESS 65纳米SRAM来扩展数据总线宽度。系统软件必须分别监视两个ERR引脚。系统设计人员可以将两个x16赛普拉斯SRAM连接到控制器的32位总线。 在这种情况下,在读取周期中,如果来自两个SRAM的ERR信号被置为有效,则必须清除并重写该SRAM器件中的数据以保持数据完整性。图7显示了这种情况下的接口方法。两个1Mx16(16-Mb)SRAM以宽度扩展模式连接,以创建1Mx32(32Mb)的存储空间。 图1 赛普拉斯SRAM接口 1.3深度扩展 在某些内存密集型应用程序中,SRAM的可用密度可能无法满足应用程序的内存要求。在这种情况下,系统设计人员可以使用赛普拉斯的65纳米SRAM进行深度扩展。 可以使用高阶地址信号(在此示例中为A20)选择SRAM,而可以连接来自两个SRAM的其余地址信号,I/O信号,控制信号和ERR信号,如图8所示。两个1Mx16(16-Mb)SRAM以深度扩展模式连接以创建2Mx16(32Mb)的存储空间。根据A20信号,一个SRAM器件被使能,另一个被禁用。禁用的SRAM器件将使其ERR引脚保持为HI-Z状态,以便活动的SRAM可以正确驱动组合的ERR信号 图2 宽度扩展和ERR

宇芯电子主要产品线有静态随机存储器SRAM,非易发性存储器MRAM,伪静态存储器PSRAM等多种类型随机记忆体及微控制器MCU等半导体产品,189-2655-4009

|

是酒窝啊

196

主题

231

回复 |

2#

在安全无线技术,连同MCU,存储器,模拟IC和USB控制器,为物联网领域提供了明显的竞争优势,并在新兴市场(包括联网设备和自动驾驶汽车)上实现了飞跃。cypress代理宇芯电子支持提供驱动、例程以及必要的FAE支持等产品服务。

宇芯电子主要产品线有静态随机存储器SRAM,非易发性存储器MRAM,伪静态存储器PSRAM等多种类型随机记忆体及微控制器MCU等半导体产品,189-2655-4009

|

|

发表于2020-10-13 16:12:58

发表于2020-10-13 16:12:58

收藏

收藏